Dan is joined by Jonathan Friedmann, a serial entrepreneur and the CEO and co-founder of Speedata. Jonathan discusses the current challenges of big data analytics and how Speedata fits into the landscape.

The views, thoughts, and opinions expressed in these podcasts belong solely to the speaker, and not to the speaker’s employer,… Read More

Frankwell Lin, Chairman of Andes Technology, started his career being as application engineer in United Microelectronics Corporation (UMC) while UMC was an IDM with its own chip products, he experienced engineering, product planning, sales, and marketing jobs with various product lines in UMC. In 1995, after four years working… Read More

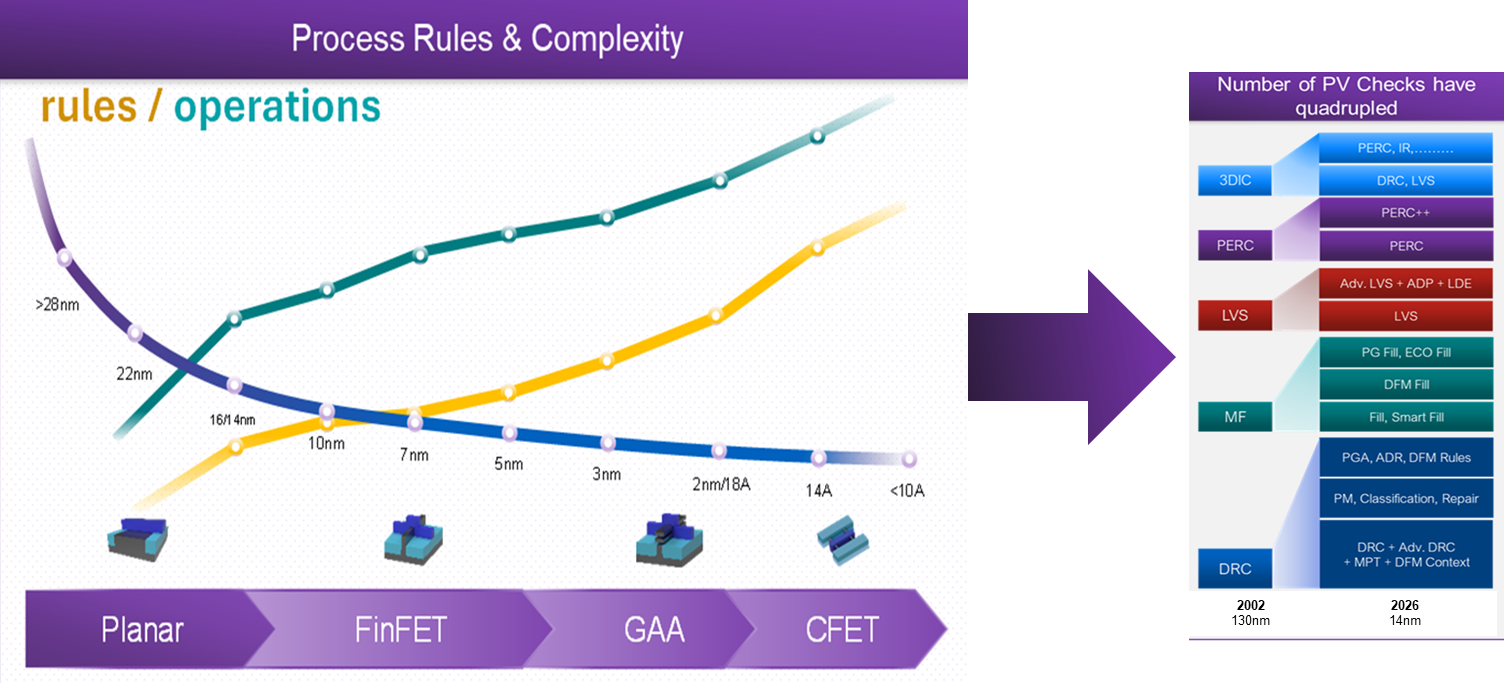

Manish Pandey, VP R&D and Fellow at Synopsys, gave the keynote this year. His thesis is that given the relentless growth of system complexity, now amplified by multi-chiplet systems, we must move the verification efficiency needle significantly. In this world we need more than incremental advances in performance. We need… Read More

5G’s Departure from Its Predecessors

In each move from 1G to 4G people became accustomed to seeing the new generation as primarily offering increased bandwidth and efficiency. It would be a mistake to view the transition to 5G along these same lines. 5G takes Radio Area Networks (RANs) from a use model primarily for cell phone communications… Read More

Now that Intel is back in the foundry business, and with the Tower Semiconductor acquisition they are definitely back in the foundry business, Samsung will be the biggest foundry loser here.

You can break the IDM foundry business into two parts: First, and foremost, the NOT TSMC Business. Second is the the Better PPA (Power/Performance,… Read More

According to the ESD Alliance, the single biggest revenue category in our industry is for semiconductor IP, so the concept of IP reuse is firmly established as a way to get complex products to market more quickly and reducing risk. On the flip side, with hundreds or even thousands of IP blocks in a complex SoC, how does a team, division… Read More

Artosyn Microelectronics, a leading provider of AI SoCs for drones and other sophisticated applications finds itself at the intersection of hardware architecture and software development. “Our customers are advancing the state of AI programming every day,” said Shen Sha, Senior R&D Manager of Artosyn’s AI Chip Department.… Read More

I viewed a recent webinar from Paul Clewes of Pulsic, and the topic was Balancing Analog Layout Parasitics in MOSFET Differential Pairs. This topic interests me, because back in 1982 I wrote my first IC layout automation tool at Intel that automatically created 15% of a GPU chip layout called the 82786, then joined Silicon Compilers… Read More

Is Intel About to Take Flight?