TSMC covered their specialty technologies in great detail. Specialty is what we inside the ecosystem used to call weird stuff meaning non-mainstream and fairly difficult to do on leading edge processes. Specialty technologies will play an even more important part of semiconductor design with the advent of chiplets where die… Read More

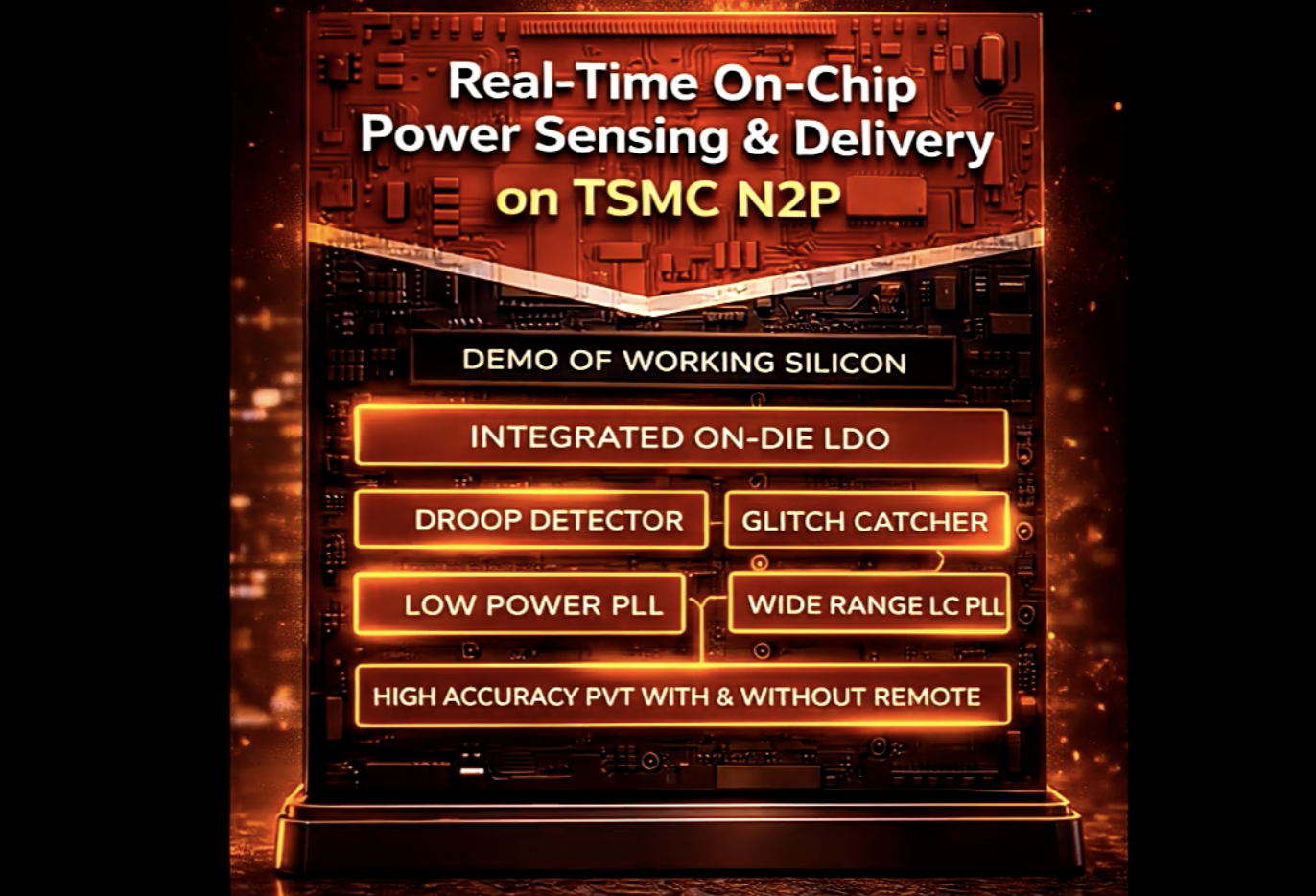

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

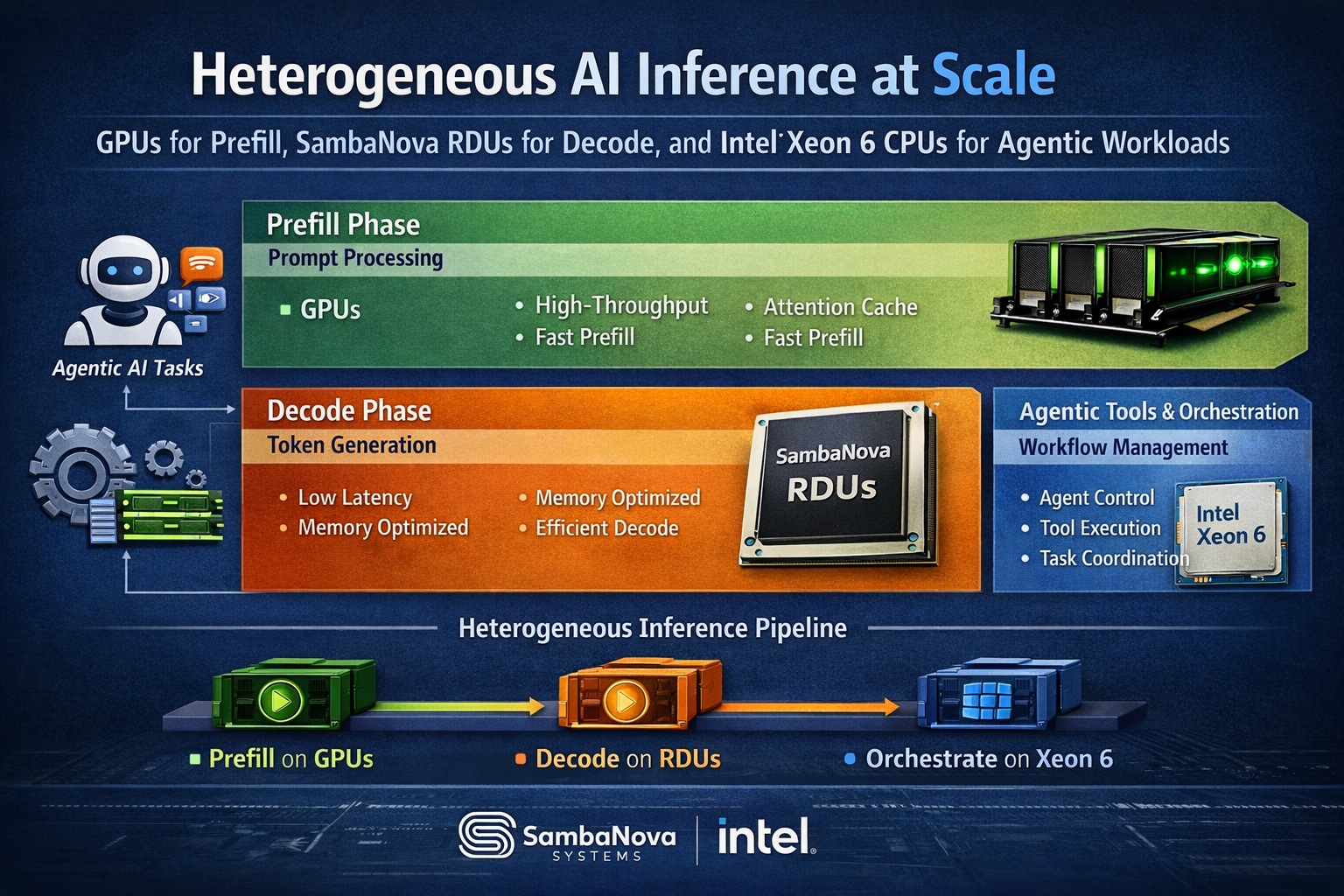

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More

CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read MoreTSMC 2023 North America Technology Symposium Overview Part 3

TSMC’s 3DFabric initiative was a big focus at the symposium, as it should be. I remember when TSMC first went public with CoWos the semiconductor ecosystem, including yours truly, let out a collective sigh wondering why TSMC is venturing into the comparatively low margin world of packaging. Now we know why and it is absolutely… Read More

TSMC 2023 North America Technology Symposium Overview Part 2

The next topic I would like to cover is an update to the TSMC process node roadmap starting with N3. As predicted, N3 will be the most successful node in the TSMC FinFET family. The first version of N3 went into production at the end of last year (Apple) and will roll out with other customers in 2023. There is a reported record amount of … Read More

TSMC 2023 North America Technology Symposium Overview Part 1

The TSMC 2023 North America Technology Symposium happened today so I wanted to start writing about it as there is a lot to cover. I will do summaries and other bloggers will do more in-depth coverage on the technology side in the coming weeks. Having worked in the fabless semiconductor ecosystem the majority of my 40 year semiconductor… Read More

Podcast EP157: The Differentiated Role Andes Plays in the US with Charlie Cheng

Dan is joined by Charlie Cheng, Managing Director of Polyhedron. Prior to that, Charlie was the CEO of Kilopass Technology, where he grew the core memory business into a successful acquisition by Synopsys. Before that, Charlie was an Entrepreneur in Residence at US Venture Partners and a Corporate VP at Faraday Technology, a Taiwanese… Read More

AI and the Future of Work

Artificial Intelligence (AI) is a rapidly growing field that has the potential to revolutionize the way we work, learn, and interact with technology. The term AI refers to the ability of machines to perform tasks that would typically require human intelligence, such as decision-making, problem-solving, and natural language… Read More

Reality Checks for High-NA EUV for 1.x nm Nodes

The “1.xnm” node on most roadmaps to indicate a 16-18 nm metal line pitch [1]. The center-to-center spacing may be expected to be as low as 22-26 nm (sqrt(2) times line pitch). The EXE series of EUV (13.5 nm wavelength) lithography systems from ASML feature a 0.55 “High” NA (numerical aperture), targeted… Read More

How to Enable High-Performance VLSI Engineering Environments

Very Large Scale Integration (VLSI) engineering organizations are known for their intricate workflows that require high-performance simulation software and an abundance of simulation licenses to create cutting-edge chips. These workflows involve complex dependency trees, where one task depends on the completion of another… Read More

Configurable RISC-V core sidesteps cache misses with 128 fetches

Modern CPU performance hinges on keeping a processor’s pipeline fed so it executes operations on every tick of the clock, typically using abundant multi-level caching. However, a crop of cache-busting applications is looming, like AI and high-performance computing (HPC) applications running on big data sets. Semidynamics… Read More

LAM Not Yet at Bottom Memory Worsening Down 50%

-Lam reported in line results on reduced expectations

-Guidance disappoints as memory decline continues

-Memory capex down 50% but still sees “further declines”

-Lam ties future to EUV maybe not good idea after ASML report

Lam comes in above grossly already reduced expectations

and misses on guidance

We always … Read More

Is Intel About to Take Flight?