Analog Bits has a way of stealing the show at every event they attend. The formula is actually quite straight-forward – come to the show with the most relevant, highest impact IP running on the most advanced process. The company will be applying this strategy again at the upcoming TSMC 2026 Technology Symposium with an array of real-time on-chip sensing and delivery IP on TSMC’s N2P process.

The latest megawatt AI and HPC systems using multi kilowatt SoCs face thermal, power efficiency, performance variability and reliability challenges that digital design alone cannot solve. Traditional approaches are no longer effective as transistors speed up and voltages scale down, creating increasing power density. Multi-chip packaging compounds power problems as well.

Addressing these power density challenges requires new approaches that leverage advanced processes along with architectural-level optimizations to achieve power targets. These are the capabilities Analog Bits will bring to the TSMC event. Let’s look a bit closer as Analog Bits demos real-time on-chip power sensing and delivery on N2P at the TSMC 2026 Technology Symposium.

The Hardware

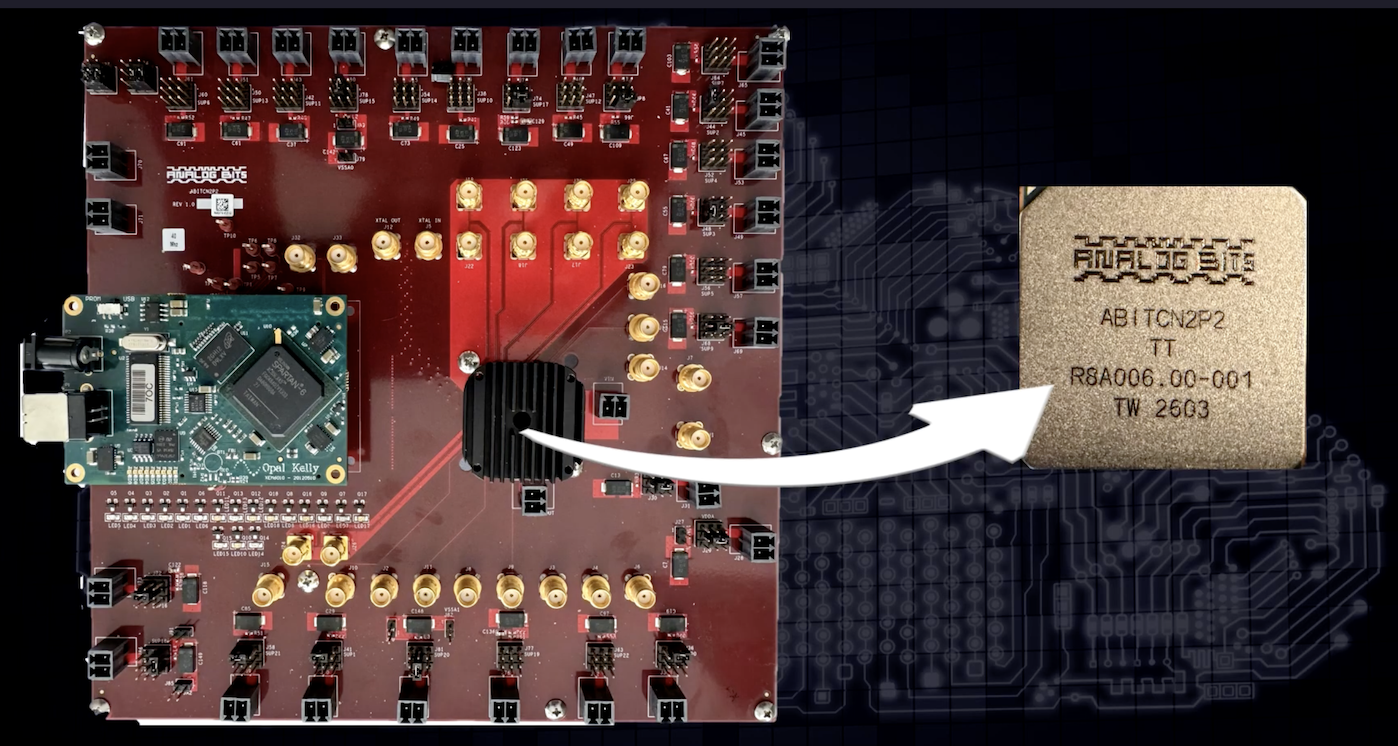

Below is a photo of the TSMC N2P test board with the test chip inserted.

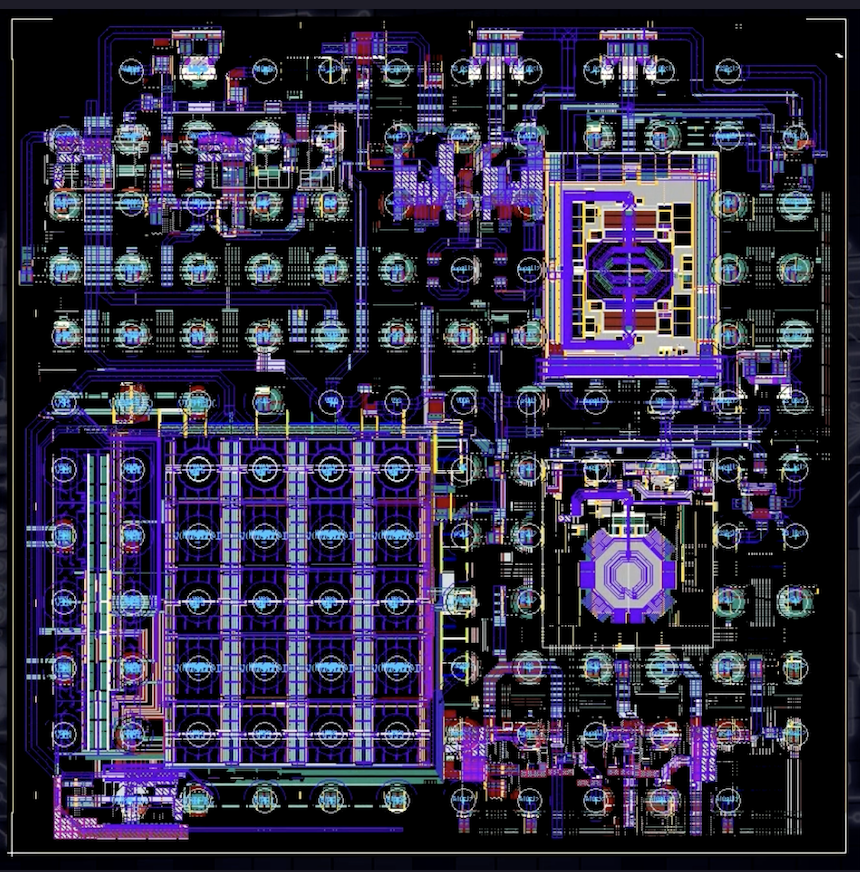

And here is the test chip layout.

The Demos

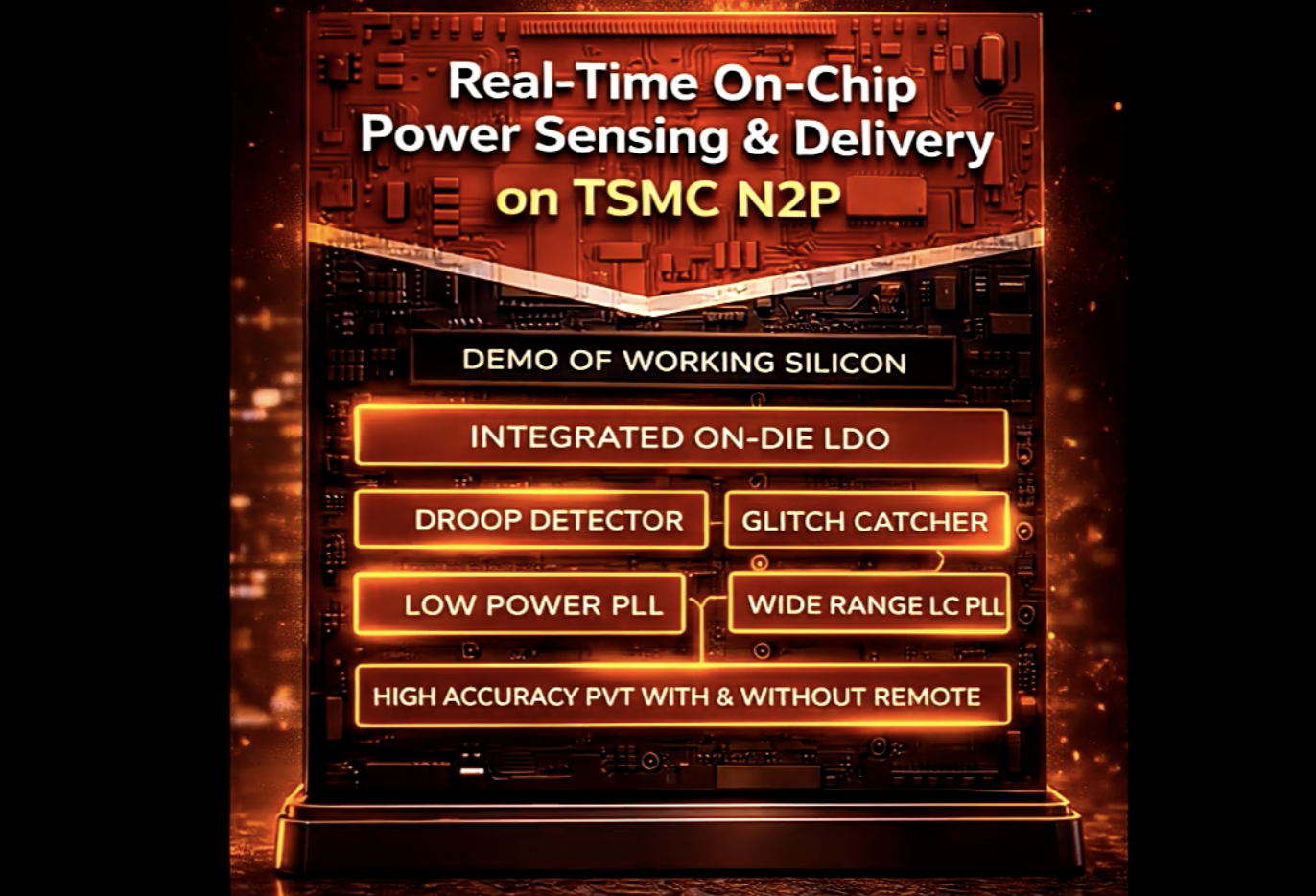

Here is an overview of some of the capabilities that you will see at the show.

LDO: A linear regulator with a small difference between input and output voltage. Example: 50-100mV. Benefits of the on-die LDO include improved power efficiency & signal integrity, fast transient response and efficient regulation, voltage scalability, integration and space savings, and noise reduction.

Target customer use cases include high-performance CPU (ARM) cores and high lane count high performance SERDES. There are multiple working silicon examples in N3P. The N2P LDO delivers a 30% area reduction and ultra-high bandwidth operation.

The Droop Detector provides an always on sensor for security hacks on TSMC N2P.

The Glitch Catcher provides high frequency detection for high reliability on TSMC N2P.

The Ultra Low Power PLL supports microwatt class low power applications on TSMC N2P.

A Low Jitter C2C PLL (up to 20GHz), ultra-low power PLL, and patented pinless core powered PLL are all available on TSMC N2P.

A high accuracy PVT sensor and pinless high accuracy PVT sensor are both available on TSMC N2P.

Also being featured for the first time are the highly accurate remote pinless PVT sensors with a +/-3.5C (untrimmed), and low power PLLs that feature microwatt class power levels at 0.5 micro-watt/MHz.

These new IPs will provide significant advantages to customers seeking PPA optimization and intelligent on-chip power management for advanced SoCs on TSMC N2P process technology. Mahesh Tirupattur, CEO of Analog Bits, commented, “Our integrated on-die LDO provide an exceptionally clean form of power delivery, coupled with the glitch catcher and droop detector features, making power observable in real-time and enabling fast corrective actions to be taken almost instantaneously.”

To Learn More

The 2026 TSMC Technology Symposium will be held on April 22, 2026, at the Santa Clara Convention Center. You can register for the event here. Be sure and stop by Analog Bits at booth #608 to see a demo of over 12 IPs on the TSMC N2P test chips. And that’s how Analog Bits demos real-time on-chip power sensing and delivery on N2P at the TSMC 2026 Technology Symposium.

Also Read:

2026 Outlook With Mahesh Tirupattur of Analog Bits

Podcast EP322: A Wide-Ranging and Colorful Conversation with Mahesh Tirupattur

Analog Bits Steps into the Spotlight at TSMC OIP

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.