The recent Chiplet Summit 2026 was a great place to learn about new chiplet designs, emerging standards, and a growing array of support technologies to help design and manufacture chiplet-based systems. In my travels at the show, I found a lot of technology that fit these descriptions. But there were also companies at the show that took a different approach to support chiplet design. We’re all aware of the importance of a well-centered design that delivers optimal performance and power consumption in the smallest footprint.

Starting with a solid design that is extensively verified before tapeout is an important step to achieve this goal. But production and real-world uncertainties can create problems for even the best design. proteanTecs is one of the companies that uses novel technology to approach this problem. Their approach delivers accurate information about the chip throughout its lifetime and takes action on this data to ensure consistent health while optimizing performance and power. And all this is done without impacting die size. Let’s take a look at how proteanTecs is changing the game for health & performance monitoring of chiplets.

My Tour Guide

I met Nir Sever, Senior Director of Business Development for proteanTecs in the company’s booth at Chiplet Summit. Nir has been with proteanTecs for over six years. Previously, he had a long history in executive management, chip design and design methodology at companies such as Tehuti Networks, 3dfx, Cadence and Zoran.

Nir explained the significant capabilities offered by proteanTecs and he demonstrated how it all worked in a live demo on the show floor with a real commercial application.

The Demo

The first point Nir covered was the scope of what proteanTecs delivers to its customers. proteanTecs is offering monitoring which is much more than the simple concept of embedded sensors. Leveraging its propriety ML-driven software engine, the software analyzes the details of the design, analyzes elements such as block size and number of clock and power domains.

Then, based on this analysis a recommended configuration of monitoring agents and Hardware (HW) Monitoring System Infrastructure is deployed. Once this configuration is agreed to, proteanTecs software does additional analysis to determine where to place each of the agents. A key point here is that this work is done *after* the design is placed and routed. So, the agents literally fit in the white space of the design thereby avoiding any additional overhead. Agent placement is an important step to optimize proximity to areas to be monitored for tight interaction between the agents.

Once implemented, the HW Monitoring System delivers critical information about the circuit without impacting die size or performance. Nir demonstrated the solution, compatible for all major implementation flows, on an Alphawave Semiconductor system with a datacenter grade high-speed optical networking chip built in a TSMC 5nm process.

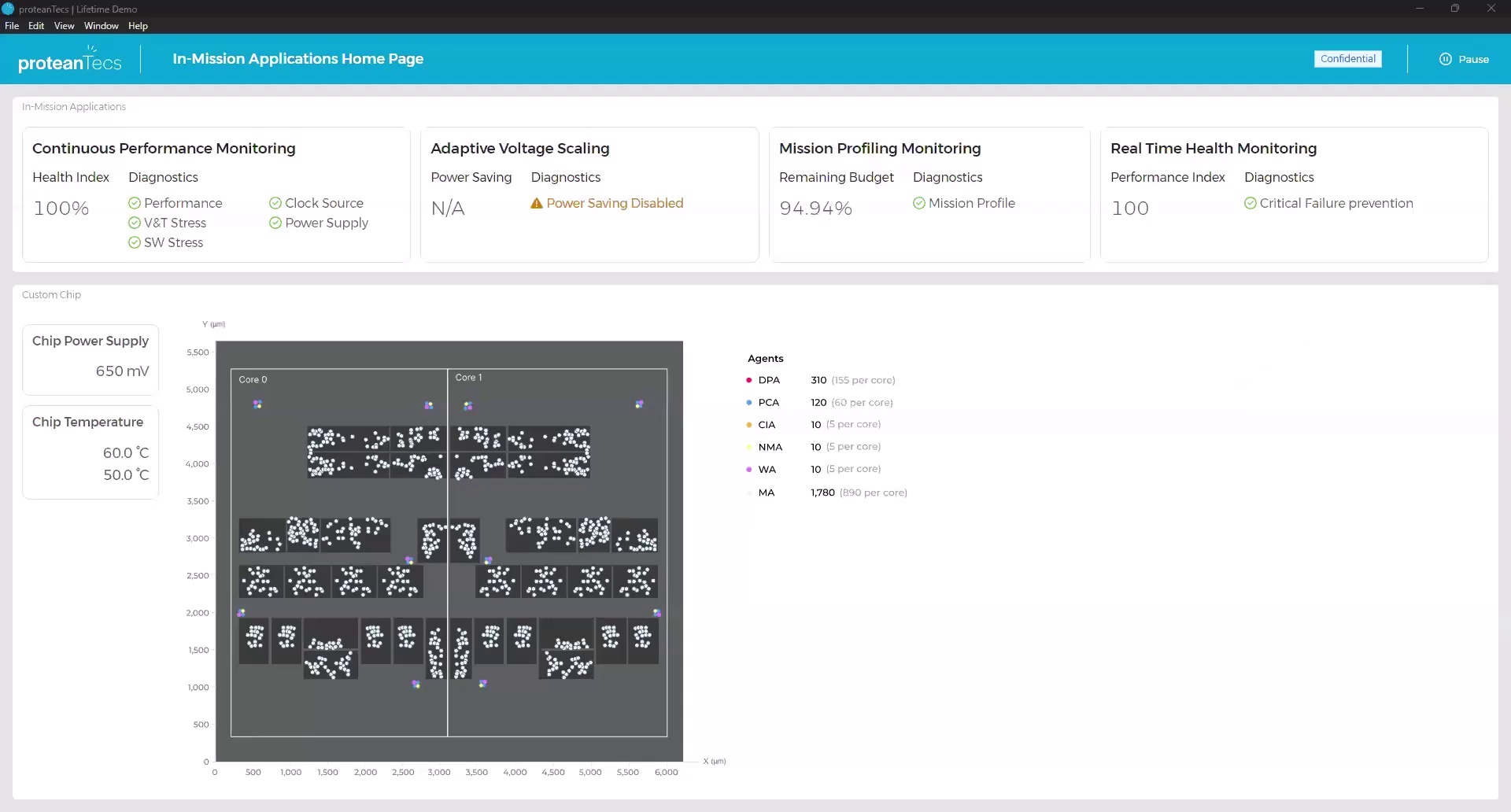

The diagram below shows the configuration and placement of the agents for the demo circuit.

Once the Agents are embedded in the design, Nir highlighted some key capabilities. The first capability he showed was Continuous Performance Monitoring. This capability reads the information from all agents periodically and visualizes it. This information is useful for system designers to help them understand how different chip configurations or workloads impact overall performance. It’s similar to a logic analyzer/virtual scope embedded in the system. The diagram below is screen capture of a fully populated display.

Margin to Timing Failure is tracking the critical path for the chip. Each of the traces in this display represent the information from one of the Margin Agents (blue dots) in the “Floorplan” figure. DC Voltage displays the voltage at various locations. V&T Stress shows the impact of voltage and temperature stress over time. Frequency depicts the stress from the toggle rate, which reflects aging in the chip. Clock Cycle-to-cycle Jitter measures noise on the clock and Effective Cycle Time Delta measures power supply noise. A complete view of chip status and behavior delivered in real time.

This mode performs passive display of the chip’s performance. Next, Nir moved to a mode where the embedded system performed active optimization and enabled adaptive voltage scaling. He explained that a typical chip operates with a voltage that has sufficient margin to ensure the chip operates correctly over its lifetime. While this strategy delivers predictable performance, it wastes power in the early stage of the chip’s lifetime, when it can safely operate at a lower voltage.

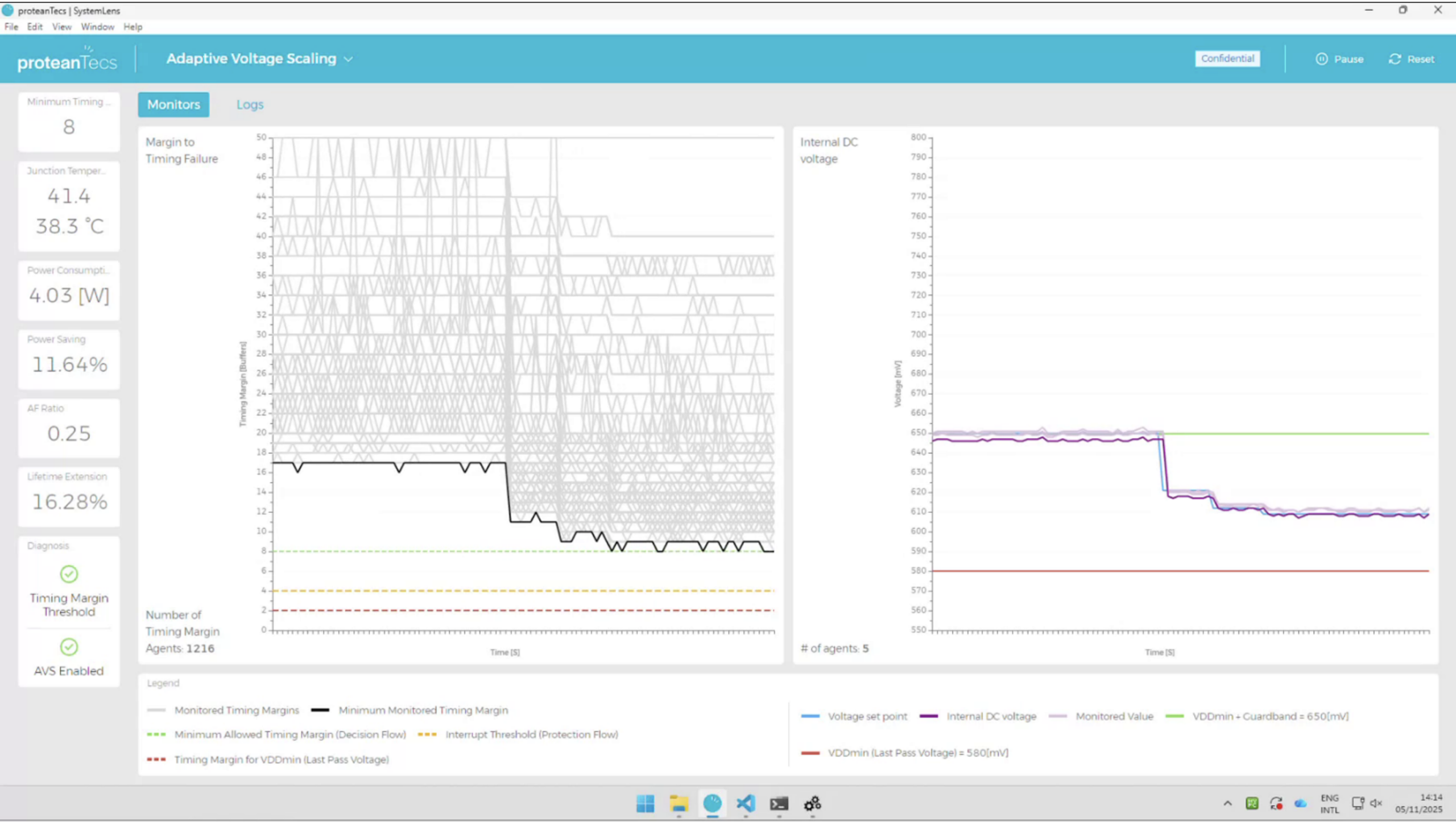

The adaptive voltage scaling function delivers the capability to “tune” the operating voltage to a safe level over the lifetime of the chip. The diagram below summarizes how this works.

The left display has the familiar Margin to Timing Failure traces. The green line below the traces shows the safe minimum timing value. You can see the system’s default operation is significantly above this value, meaning it is operating at an unnecessarily high voltage. The system then begins to lower the operating voltage as shown on the right. This continues until the chip is operating at the lowest safe timing threshold. On the far left, you can see a power saving of 11.64% has been achieved. And because the chip is operating at a lower voltage the lifetime of the chip has been extended by 16.28%. Nir explained that the code to perform this optimization is embedded in the on-chip application. It is completely self-contained and requires no external cloud access.

For demonstration of the safety-net, Nir forced a lower operating voltage to drive the system below the safe operating margin. Within two clock cycles the problem was sensed and corrected, keeping the chip exactly at the minimum safe operating point. This is one of many potential applications that can be deployed using proteanTecs. Nir explained that customers can develop their own applications as well. Since most of the processing is done on the embedded hardware, the size of a typical application is quite small at 10 – 50 kilobytes. It became clear to me that the proteanTecs technology delivers safe, robust operation across the lifetime of the chip with very little overhead.

To Learn More

During my time with Nir at the proteanTecs booth I saw an impressive demonstration of what proteanTecs can deliver to optimize any design over its lifetime. This discussion only scratches the surface of what the company offers.

You can learn more on their power reduction solution and AVS Pro here. You can also learn more about the depth of extensive capabilities offered by proteanTecs here. And that’s proteanTecs at Chiplet Summit – changing the game for health & performance monitoring of chiplets.

Also Read:

Intelligent Networks: Power, Reliability, and Maintenance in Telecom — Webinar Preview

Accelerating NPI with Deep Data: From First Silicon to Volume

Failure Prevention with Real-Time Health Monitoring: A proteanTecs Innovation

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.