proteanTecs is a unique company, delivering electronics visibility from within. Its core mission is to enable the electronics industry to continue to scale. The company achieves this goal by first embedding on-chip monitors, called Agents, during the design process to generate deep data on the chip’s profiling, health, and performance. Machine-learning algorithms process this on-chip data throughout the device’s lifecycle, in both test and mission modes. Users gain deep data analytics with actionable insights and alerts on a cloud-based platform with edge applications on the automated test equipment (ATE) or embedded on the board itself.

It’s well-known that power optimization is a huge and growing problem across many markets, so the application of this unique technology to this problem holds great promise. Read on to learn how proteanTecs is addressing the power consumption challenge.

Overview of the Power Reduction Solution

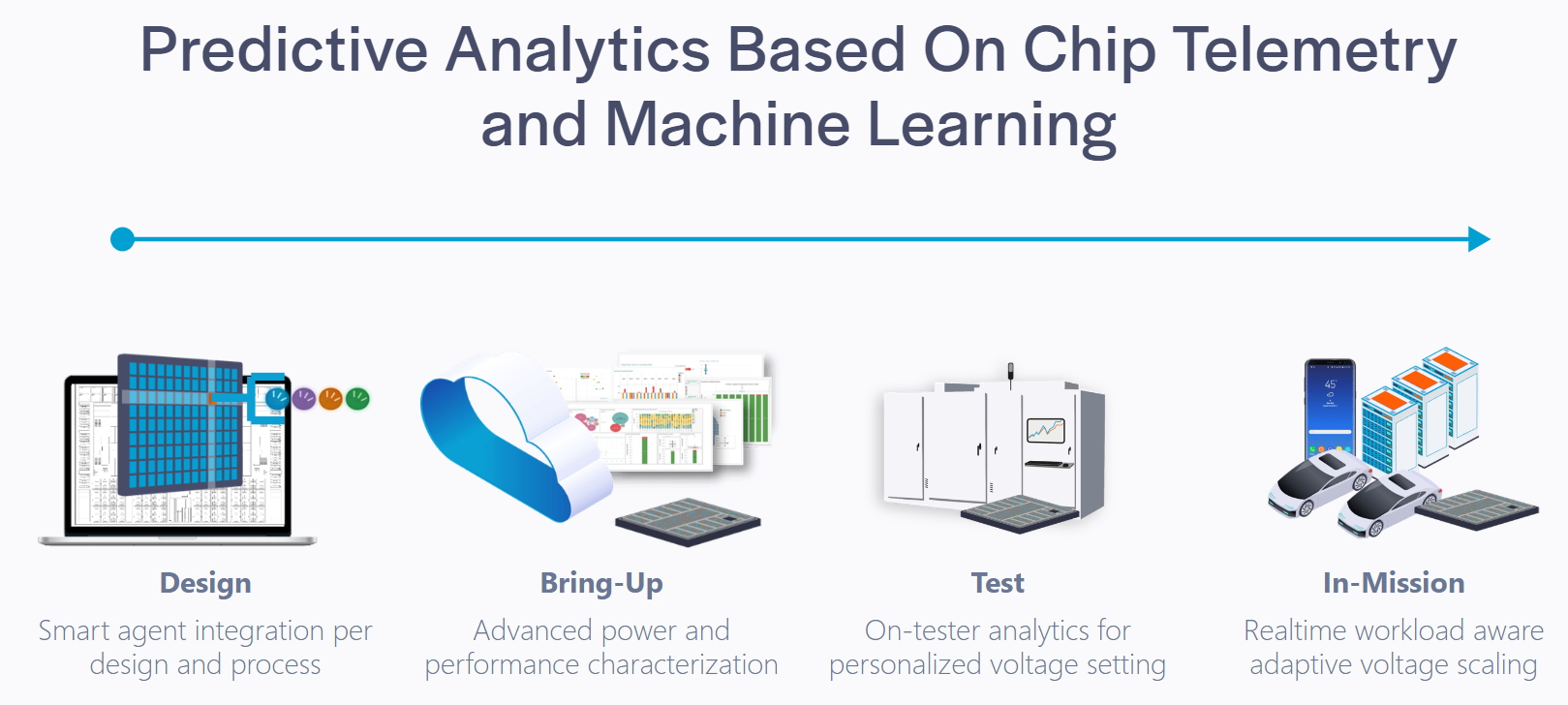

Recently, proteanTecs announced a new power reduction solution aimed at high-performance markets. Using its proven technology, chip makers and system operators can now optimize power and performance without the risk of system failure. This unique capability uses on-chip telemetry, machine learning and predictive analytics to enable workload-aware system-on-chip (SoC) power reduction during production testing and in-field operations.

For in-field power savings, proteanTecs introduced AVS Pro™, a real-time application for functional-workload aware adaptive voltage scaling (AVS). Based on timing margin Agents, AVS Pro leverages excessive guard-bands to reduce power while guaranteeing failure prevention. This capability is silicon-proven in leading-edge technologies and has enabled customers to reduce power consumption by an average of 8-14%.

For power reduction during production, proteanTecs offers prediction-based VDDmin optimization per individual chip and system, with deep data analytics for process grading. These applications are deployed on the tester with advanced analysis on the proteanTecs cloud platform. Partnering with leading ATE vendors, parametric power and performance visibility for inline decision making is enabled.

The technology finds application across a broad range of reliability-critical markets, such as cloud computing, mobile, telecommunications and automotive. The figure below provides an overview of how the pieces fit together.

Case Study of Use in a Real Design

Results in a real design project are the most compelling proof for any new optimization technology. proteanTecs has made a detailed case study available to demonstrate impact. Some key details and achievements disclosed in this case study include:

- The customer is a fabless chipmaker making 5nm networking chips for datacenters

- The challenge faced by this customer was high power consumption due to excessive voltage guard-bands

- Using proteanTecs AVS Pro, power optimization with a safety-net was achieved in real-time

- The result was a 12.5% dynamic power reduction which translates into more than $5M per year energy cost savings for hyperscale cloud vendors

- An 11% performance increase was also achieved because of a higher utilization rate per system

There is more to this impressive story. You can download a complete copy of the case study here.

To Learn More about proteanTecs AVS Pro

Application-specific power performance optimization based on chip telemetry embodies many moving parts to realize the complete solution. The proteanTecs’ AVS Pro application monitors the margin to timing failure of millions of real paths, in real time, under real workloads, to reduce voltage to the lowest point that still allows error-free functionality. It also provides an inherent safety-net to prevent failures when events like voltage drops occur, while enabling fast frequency and voltage scaling.

The company has published a comprehensive white paper that dives into the details of how its technologies are combined to deliver these results. The piece covers the power, performance, reliability equilibrium that can be achieved with properly developed guard bands. The various approaches to dynamic power management are also discussed. The AVS Pro solution is explained in detail to illustrate how significant power reduction can be achieved. You can download your copy of this very informative white paper here.

Calculate Your Savings

If you visit the power reduction solution web page, there is a calculator to help you estimate the improvements that are possible for CPU, GPU and AI accelerator chips in the datacenter. If power optimization is a concern for a current or next design, I highly recommend you check out the savings that are possible.

Also Read:

Fail-Safe Electronics For Automotive

Building Reliability into Advanced Automotive Electronics

Unlocking the Power of Data: Enabling a Safer Future for Automotive Systems

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.