As SoC and IP designs continue to increase in complexity while schedules accelerate, verification teams are looking for methodologies to improve design confidence more quickly. Formal verification techniques provide one route to improved design confidence, and the increase in papers and interest at industry conferences… Read More

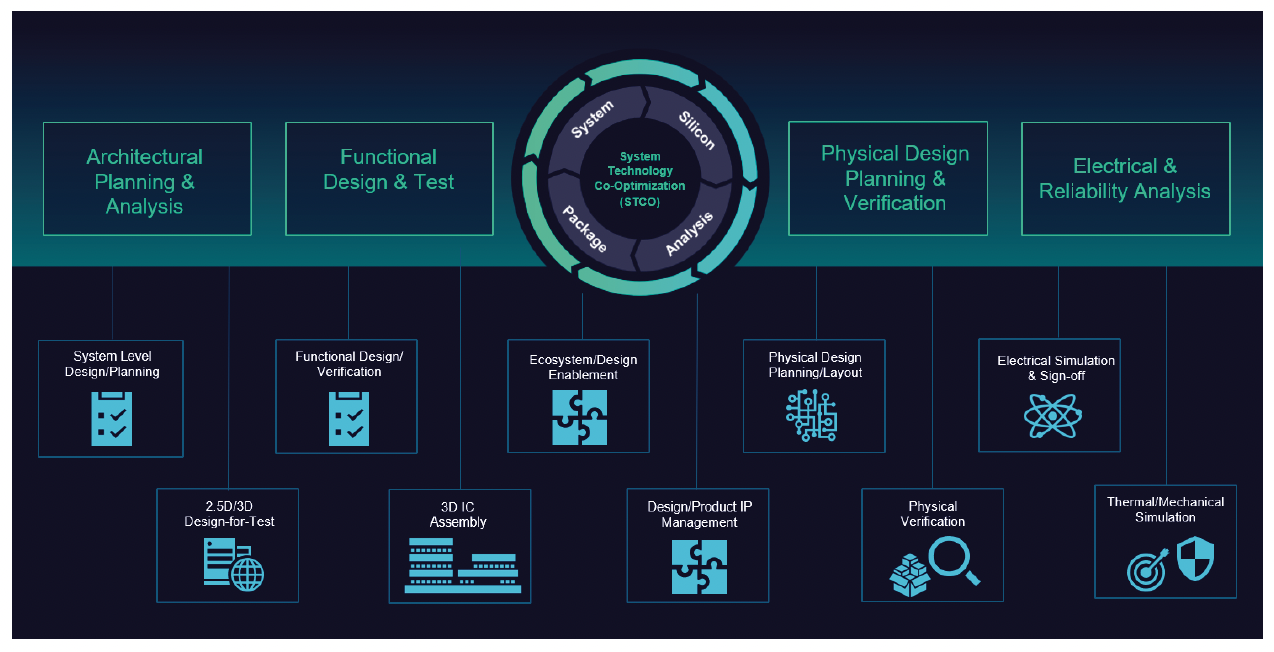

Enabling the Ecosystem for True Heterogeneous 3D IC DesignsThe demand for higher performance, greater configurability, and…Read More

Enabling the Ecosystem for True Heterogeneous 3D IC DesignsThe demand for higher performance, greater configurability, and…Read More Why I Think Intel 3.0 Will SucceedProbably one of the most anticipated semiconductor investor…Read More

Why I Think Intel 3.0 Will SucceedProbably one of the most anticipated semiconductor investor…Read More Griffin Securities’ Jay Vleeschhouwer on EDA Acquisitions and StartupsJay Vleeschhouwer, Managing Director of Software Research at…Read More

Griffin Securities’ Jay Vleeschhouwer on EDA Acquisitions and StartupsJay Vleeschhouwer, Managing Director of Software Research at…Read More Security Coverage: Assuring Comprehensive Security in Hardware DesignAs hardware systems become increasingly complex and security…Read More

Security Coverage: Assuring Comprehensive Security in Hardware DesignAs hardware systems become increasingly complex and security…Read More Scaling 3D IC Technologies – Siemens Hosts a Meeting of the Minds at DAC3D IC was a very popular topic at…Read More

Scaling 3D IC Technologies – Siemens Hosts a Meeting of the Minds at DAC3D IC was a very popular topic at…Read MoreEmbeddable FPGA Fabric on TSMC 7nm

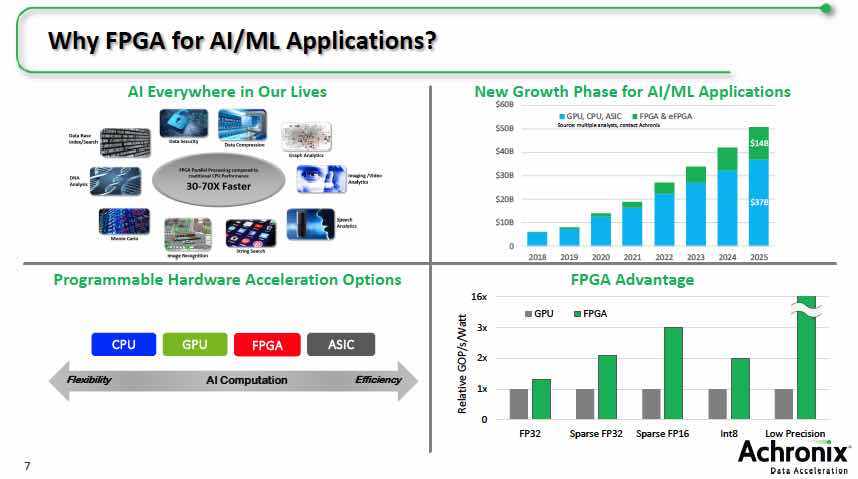

With their current line-up of embeddable and discrete FPGA products, Achronix has made a big impact on their markets. They started with their Speedster FPGA standard products, and then essentially created a brand-new market for embeddable FPGA IP cores. They have just announced a new generation of their Speedcore embeddable… Read More

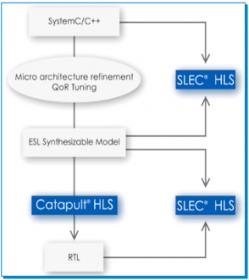

Sequential Equivalency Checks in HLS

Higher level synthesis (HLS) of an IP block involves taking its high-level design specification –usually captured in SystemC or C++, synthesizes and generates its RTL equivalent. HLS provides a faster convergence path to design code stability, promotes design reuse and lowers front-end design inception cost.

HLS and Mentor… Read More

Big Data Analytics in Early Power Planning

ANSYS recently hosted a webinar talking about how they used the big-data analytics available in RedHawk-SC to do early power grid planning with static analytics, providing better coverage than would have been possible through pure simulation-based approaches. The paradox here is that late-stage analysis of voltage drops … Read More

DVCon is coming in February, now is the time to register early

As 2018 wraps up this month it’s time to start thinking and planning for 2019, and if you work in the Silicon Valley then you’ll want to consider adding the 31st annual DVCon event planned for February 25-28 in San Jose. Surveys have shown for some time now that verification tasks actually take up more time on a SoC project… Read More

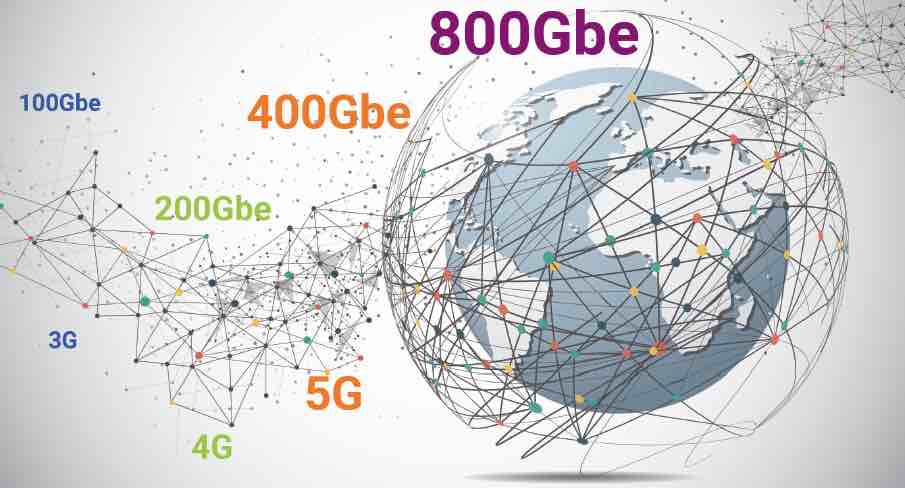

56G and 112G SerDes Where the rubber meets the road

No matter how high the processing capability of a chip, its overall performance is limited by IO speed. This is very similar to a car with low performance tires, a powerful engine will not be able to transfer its energy to the ground effectively. There is quite literally a race going on between core processing and IO speeds for transferring… Read More

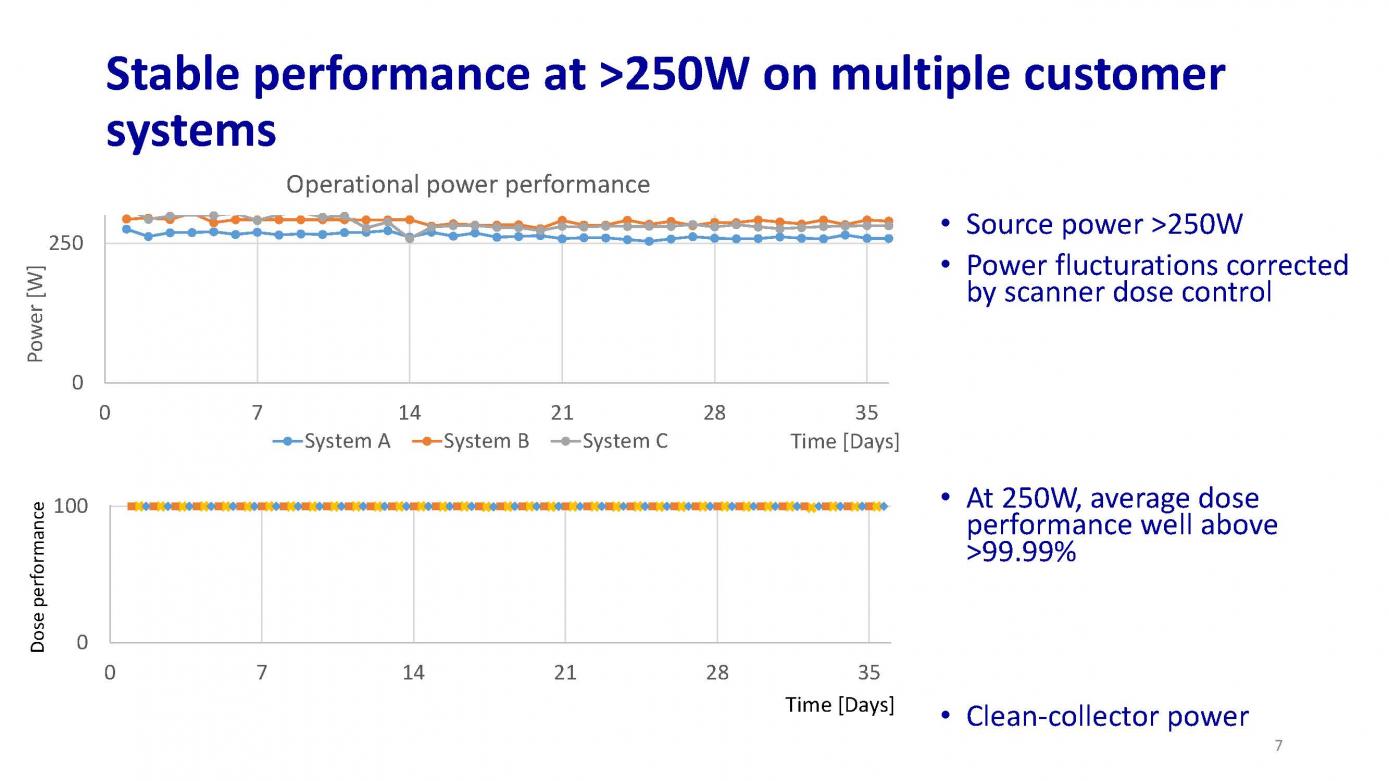

IEDM 2018 – ASML EUV Update

At IEDM last week Anthony (Tony) Yen, Vice President and Head, Technology Development Centers Worldwide for ASML presented a paper entitled “EUV Lithography at Threshold of High-Volume Manufacturing” authored by Anthony Yen, Hans Meiling, and Jos Benschop. At IEDM I had a chance to sit down with Tony and discuss the paper and … Read More

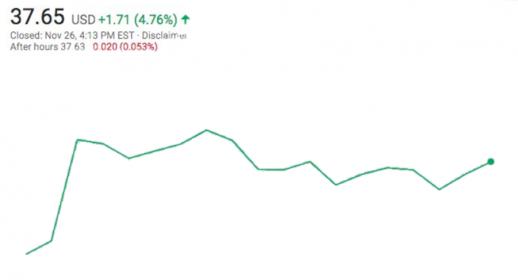

Changes Coming at the Top in Semiconductor Equipment Ranking

Semiconductor equipment vendor ranking, which didn’t change much between 2016 and 2017, is undergoing a makeover, as Lam Research, ASML, and Tokyo Electron (TEL) are switching places and top-ranked Applied Materials is getting closer to losing its number one ranking.

Since the 1990s, Applied Materials has been the market leader… Read More

IEDM 2018 Trip Report!

Hello, my name is Daniel Nenni and I am a semiconductor conference addict. I just can’t seem to get enough. The semiconductor ecosystem is very wide now and moves so quickly it is nearly impossible to keep up without constant conference attendance. As a SemiWiki contributor not only do I get free conference passes, I get access to … Read More

GM: Stop the Downsizing!

General Motors CEO Mary Barra is known for a number of quotes one of which is: “My father was a die maker for 39 years, so I had a basic understanding of the automobile industry and what the manufacturing world was like, just from the opportunity to spend time with him, just talking, because he was a car buff.” One has to wonder what Mary’s… Read More

Musk’s new job as Samsung Fab Manager – Can he disrupt chip making? Intel outside