I recently watched a webinar titled “How to accelerate power-aware simulation debug with Synopsys’ VC LP” that was presented by Ashwani Kumar Dwivedi senior applications engineer at Synopsys. Watching the webinar made me reminisce how design verification has evolved over the years. A long time ago, static verification started gaining attention as a way to address some of the challenges of those times. Performance and memory capacity of computers couldn’t meet the turnaround time demands of simulating complex designs. And after long turnaround time simulations, if design bugs were identified, it was a gargantuan task to debug.

Static verification tools were developed to pre-verify designs. A way to catch design bugs early-on and minimize the need for running elaborate dynamic simulations as a requirement for signoff. Results were amazing and there was even a push for signing off simple designs without even running dynamic simulations or simply running dynamic simulations with a small set of test vectors just to exercise the complex portions of the designs. Nowadays, with the increased design complexities, SoC designs, incorporation of extreme low power design techniques and access to high performance compute/memory capacity, tendency may be to rely more heavily on dynamic simulation.

This webinar showcases how a judicious combination of static verification and dynamic simulation can provide immense benefits. The presenter provides lots of examples to highlight each area of benefit and quantifies the benefits using results from some case studies. I recommend you watch the webinar to get the complete details.

I’ll synthesize below what I gathered from watching the webinar.

First things first. The webinar sheds light on lot more aspects than what the webinar title may suggest. It addresses more than just accelerating simulation debugging. It covers issues that lead to down-stream bugs that show up during simulation and discusses ways to prevent those bugs in the first place.

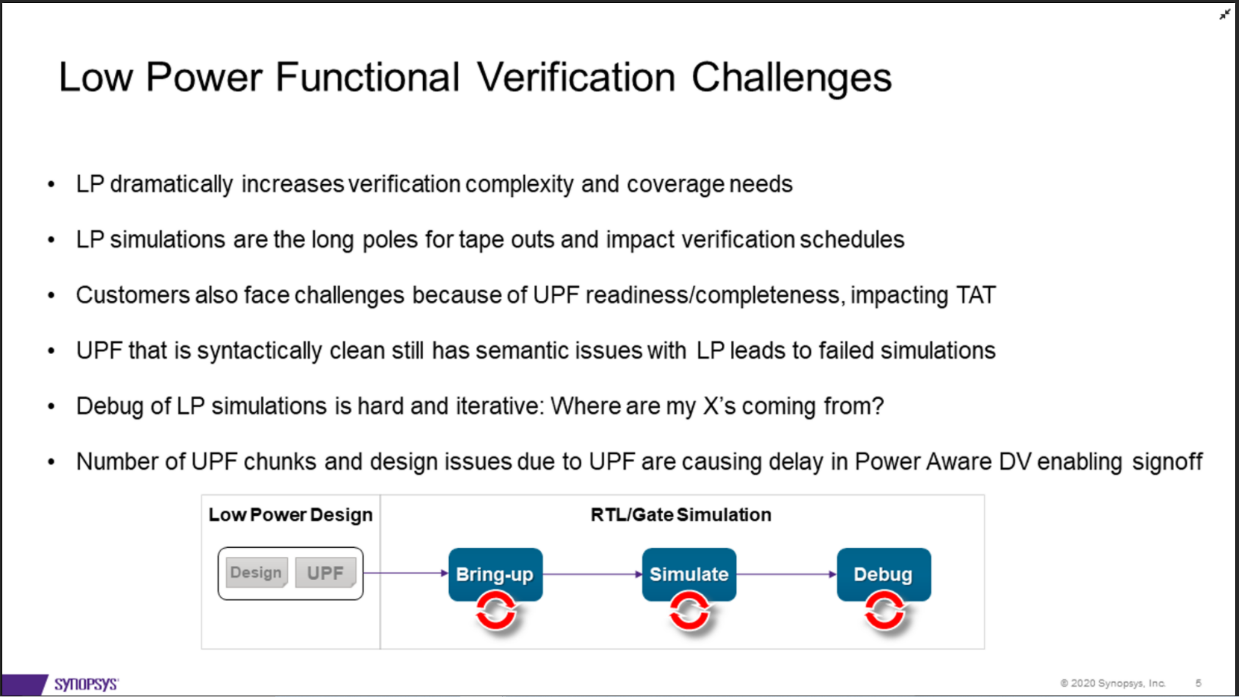

The presenter sets the stage (Figure 1) by listing the many challenges faced during low power functional verification that fall into the Bring-up, simulation and debug stages. The fewer number of iterations that happen in each of these stages, the faster the turnaround time to design signoff.

Figure 1 (Source: Synopsys)

He highlights the importance of running a design independent UPF check (DIUC). Many UPF issues that have the potential to cause down-stream problems can be caught independent of the design and it is very important to fix these even before getting Synopsys VC LP to run.

Presenter then discusses many examples of situations where custom design rules are needed and if not implemented will cause bigger debug challenges down-stream. He walks through some examples and talks about VC LP custom design rule writing and checking functionality that is not possible with just UPF.

He then addresses how LP architecture checks can be performed for detecting both structural and functional issues. Debugging simulation failure due to X-propagation is very challenging and time consuming. The presenter goes into details of the many reasons that lead to X-propagation in simulation that can be prevented from entering the simulation stage.

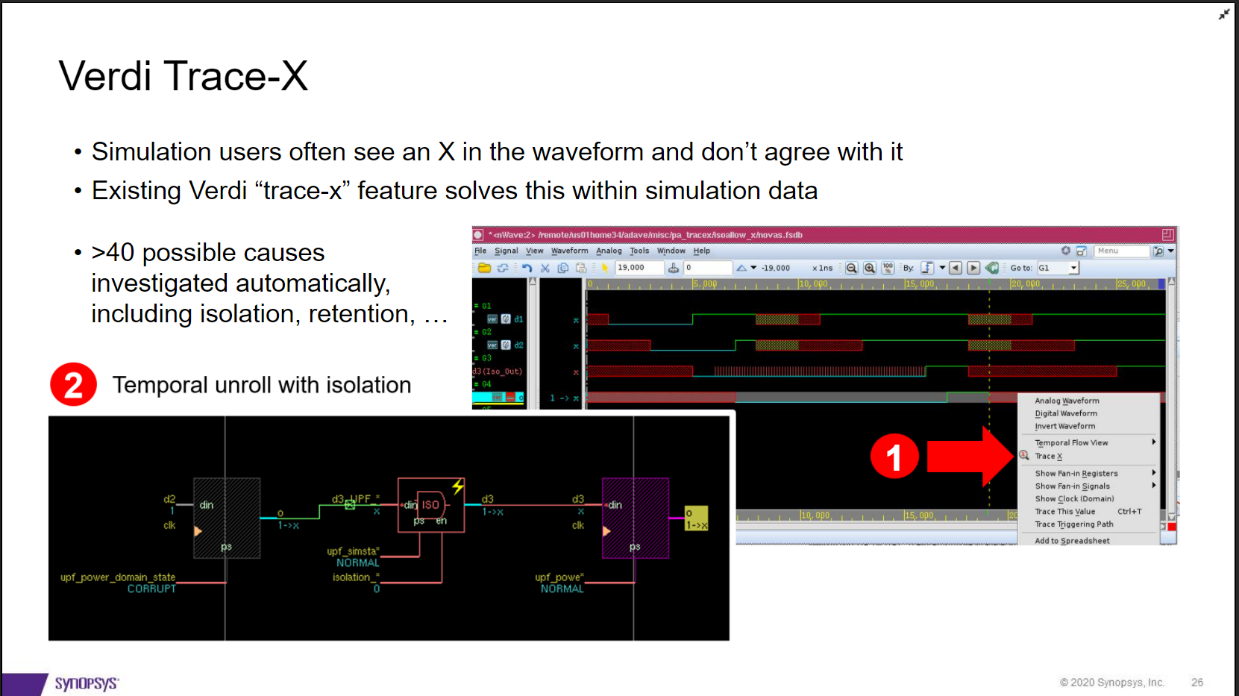

The integrated flow between Synopsys VCS® and VC LP makes it an almost zero effort task for the simulation team to run VC LP. The presenter advises that whenever possible, the same team should run both static verification and simulation. This combined with an integrated flow through Synopsys’ Verdi® HW SW Debug software (Screenshot in Figure 2) enables easy tracing of debug situations for locating their root causes.

Figure 2 (Source: Synopsys)

By leveraging VC LP with VCS, a lot can be gained in terms of time and cost savings. The presenter reports stats from some case studies where a 38% reduction in simulation run time and an 81% reduction in design related issues were achieved after running VC LP ahead of simulation.

Check out the full webinar to see detailed examples and how they are applicable to your particular role within the design cycle.

Also Read:

A New ML Application, in Formal Regressions

Change Management for Functional Safety

What Might the “1nm Node” Look Like?

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.