I recently watched a webinar titled “How to accelerate power-aware simulation debug with Synopsys’ VC LP” that was presented by Ashwani Kumar Dwivedi senior applications engineer at Synopsys. Watching the webinar made me reminisce how design verification has evolved over the years. A long time ago, static verification started… Read More

Tag: low power design

Navigating Memory Choices for Your Next Low-Power Design

Choosing a memory architecture can be a daunting task. There are many options to choose from, each with their own power, performance, area and cost profile. The right choice can make a new design competitive and popular in the market. The wrong choice can doom the whole project to failure.

Vadhiraj Sankaranarayanan, senior technical… Read More

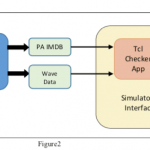

Tcling Your Way to Low Power Verification

OK – maybe that sounds a little weird, but it’s not a bad description of what Mentor suggests in a recent white-paper. There are at least three aspects to power verification – static verification of the UPF and the UPF against the RTL, formal verification of state transition logic, and dynamic verification of at least some critical… Read More

Low Power Design – Art vs. Science

I have heard many times before that low power and mixed-signal design is more Art than Science. I believe this is a misconception. Science is a field that builds upon previous experiences and discoveries. Art primarily seeks out creative differences, things we have not seen before that evoke emotion. The most successful designers… Read More

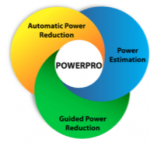

Power Exploration at RTL Design with Mentor PowerPro

There was a comment recently that design for low power is not an event, it’s a process; that comment is absolutely correct. Power is affected by everything in the electronic ecosystem, from application software all the way down to layout and process choices. Yet power as a metric is much more challenging to model and control than … Read More

Free Webinar: Designing Low-Power IoT Systems

As I have written before, IoT looks to be a key driver for design starts and future semiconductor revenue growth which is why we wrote “PROTOTYPICAL” and included a field guide to FPGA Prototyping. If you want to get funding for your new IoT chip project, having a working prototype is a good thing, absolutely. If you want to take a look… Read More

Have We Hit the Power Floor?

As we celebrate the 50[SUP]th[/SUP] anniversary of the publication of Moore’s Law in Electronics Magazine (April 19, 1965), the industry finds itself in an increasingly costly global effort to keep transistor scaling on track. “Is Moore’s Law dead?” is a common question these days.

But practically speaking the doubling of transistor… Read More

Low Power @ DesignCon 2014

Taking place annually in Silicon Valley, DesignCon is the premier educational conference and technology exhibition for electronic design engineers in the high speed communications and semiconductor communities.

Created by engineers for engineers, DesignCon is the largest gathering of chip, board and systems designers… Read More

Customer Stories at DAC#50

When you think Apache Design you probably think Low Power Design and what stuffed animal will they give away at DAC. The other thing you should think about is how the top semiconductor companies around the world use Apache products for leading edge semiconductor design. Demos are fine, but there is nothing like talking directly … Read More

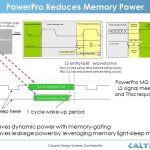

Dynamic/Leakage Power Reduction in Memories

Embedded memories have an important impact on power. SoCs that integrate multiple functions on a single silicon die are at the heart of many electronic devices. As process geometries have scaled, design teams have used more and more of the additional silicon real estate available to integrate embedded memories that serve as scratch-pads,… Read More