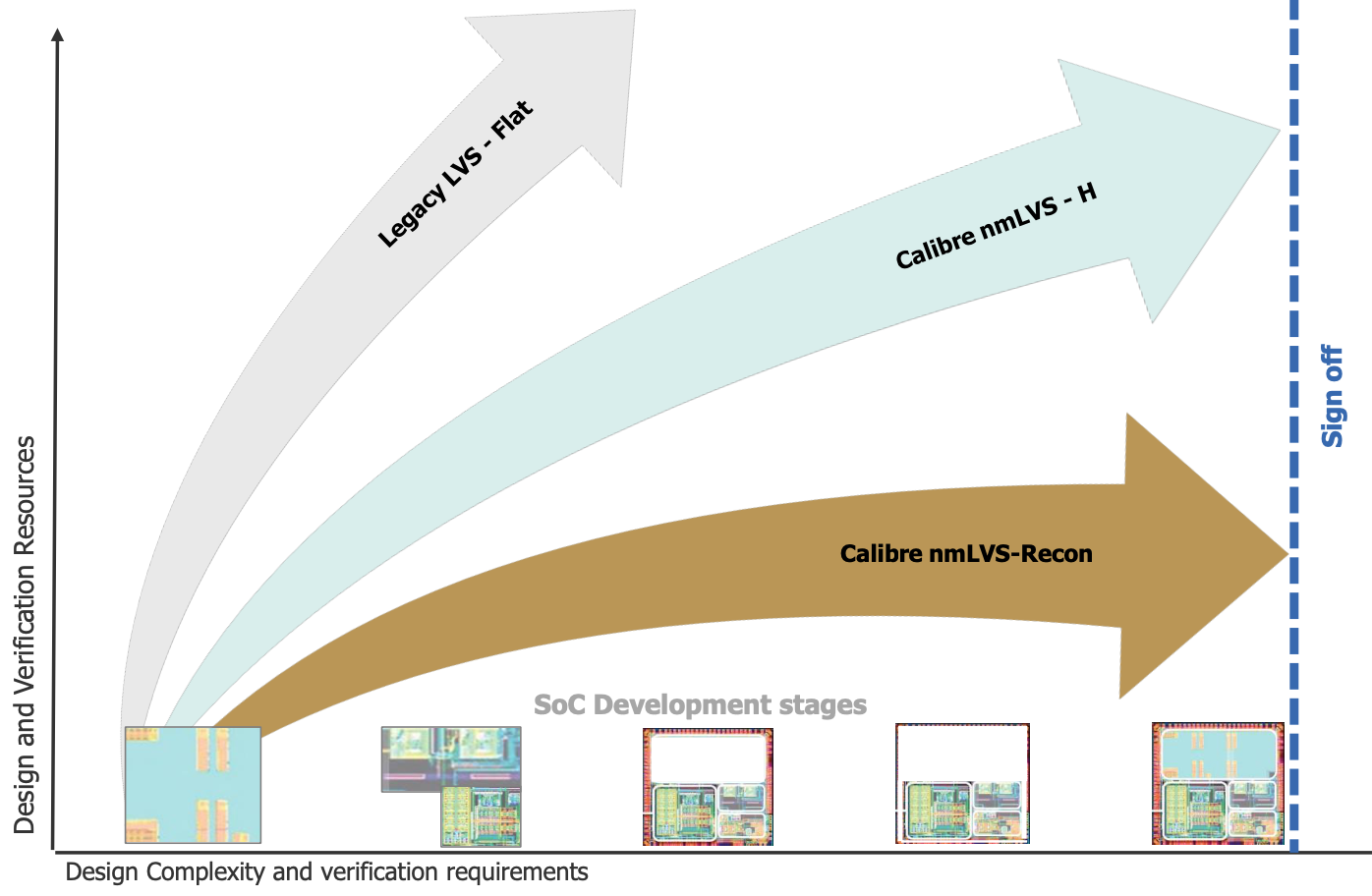

Most of us will remember the productivity boost that hierarchical analysis provided vs. analyzing a chip flat. This “divide and conquer” approach has worked well for all kinds of designs for many years. But, as technology advances tend to do, the bar is moving again. The new challenges are rooted in the iterative nature of high complexity design.

A typical design has many, many blocks that all mature on different schedules. Nonetheless, these blocks need to be verified as they mature and there’s the rub. Called “dirty” designs, early versions of a complex chip are missing lots of detail. This creates a problem since certain checks are appropriate for these early designs, but others will generate huge numbers of false errors thanks to the incomplete nature of the circuit. Debugging some early design issues, such as shorts, can be incredibly time-consuming as well since a short can impact a huge part of the network.

Mentor has come up with a way to deal with these problems. It’s called Recon technology and the company recently announced the addition of the technology to its Calibre nmLVS product. I had the opportunity to get a briefing on this new technology from Hend Wagieh, Sr. Product Manager of Circuit Verification, Calibre Design Solutions at Mentor.

Hend explained the new Recon technology had its launch last year at DAC 2019 with Calibre nmDRC-Recon. DRC has similar challenges with incomplete designs and Calibre nmDRC provides a 6X – 12X performance boost for early checks. Hend began by reviewing the complexity challenges that new nodes, such as 5nm, present:

- Circuit verification rules have become more complex

- More devices and polygon counts

- More dummy devices added

- More device parameters and compounded calculations

- Rules expanding in scope

- Context sensitivity

- Color-awareness

- FinFETs

- Retargeting

- Multi-patterning

This complexity coupled with the incomplete nature of early designs spells big trouble for LVS unless there is some intelligence applied. This is where the Recon technology essentially provides a paradigm shift for LVS. The new approach can be summarized as follows:

Objective: Only execute what’s necessary to resolve early design main pain points

- Categorization: Focus on specific types of violations

- Prioritization: Address the most impactful errors first

- Task Distribution: Allow teams to focus on specific set of design issues

- Partitioning: Split data for easier debugging and root cause analysis

Hend described something called “Minimum Selective Extraction”. The Recon approach basically sorts all error checks into early and late design versions and applies intelligence regarding the way early design checks are done to minimize run time and maximize identification and correction of real errors. The result is faster early run times and cleaner late checks.

Hend spent some time discussing short paths in early (dirty) designs. She explained that an average-size early design could have about 20K short paths, with a short in the power/ground grid extending throughout the entire chip. A customer has reported spending 80% of their verification cycle debugging shorts, with complex shorts taking weeks to fix.

Using Recon technology, this problem can be managed very effectively, with up to 30x faster iterations and 3x leaner hardware usage. The results are quite dramatic.

A customer perspective was provided in the press release:

“The Calibre nmLVS-Recon approach establishes an entirely new paradigm for circuit verification use models,” said Jongwook Kye, vice president of Design Enablement Team at Samsung Electronics. “By combining the Calibre nmLVS-Recon technology with Samsung’s existing certified sign-off Calibre nmLVS design kits, our mutual customers will experience faster iterations on early ‘dirty’ designs, driving accelerated LVS verification cycles. All of this will help mutual customers tape out sooner at Samsung.”

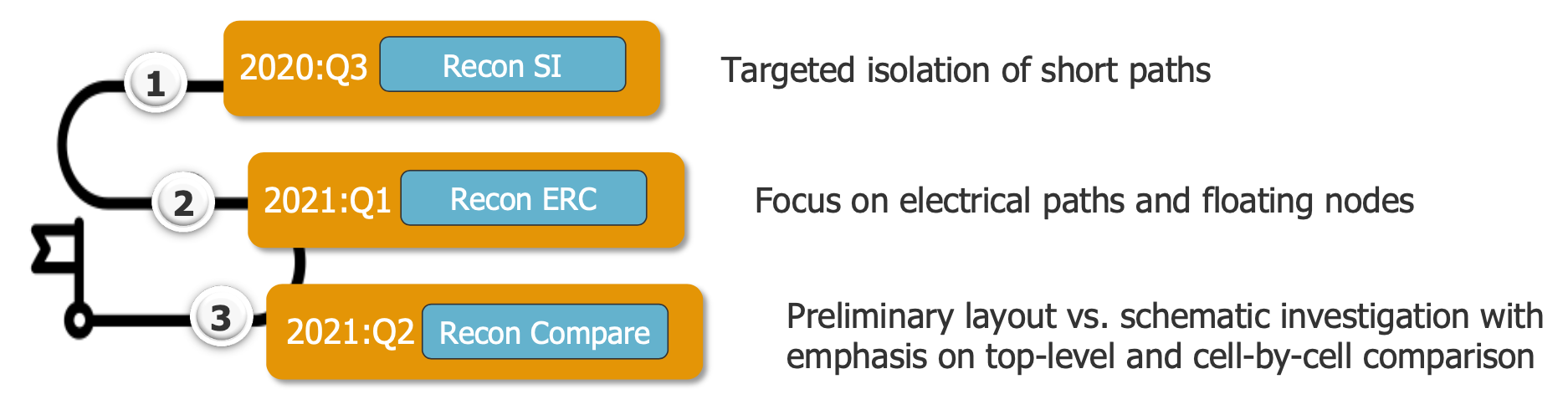

The Calibre nmLVS-Recon flow can be used with any foundry/integrated device manufacturer’s (IDM) Calibre sign-off design kit “as is,” and on any process technology node. The product will be released in phases as shown in the diagram below.

The Calibre nmLVS-Recon initial offering will be available to the market with the Calibre family release in July of 2020, with planned additional capabilities in later releases. For more information please visit: https://bit.ly/2ZA7qjn.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.