The much anticipated (virtual) DVCON 2022 is happening this week and functional verification plus UVM is a very hot topic. Functional Verification Engineers using UVM can enjoy a large number of benefits by synthesizing test content for their testbenches. Abstract, easily composable models, coverage-driven content, deep sequential state exploration, pre-execution randomization for test optimization and configurable reuse are just some examples of the advantages afforded by test suite synthesis.

However, a specification model is required and there are few alternatives that a UVM/SystemVerilog engineer can simply pick up and use.

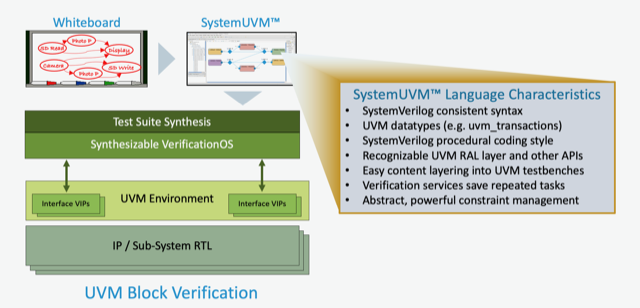

Enter SystemUVM™, a UVM class library built on top of Accellera’s Portable Stimulus Standard that looks and feels like SystemVerilog with UVM, but enables the level of abstraction and composability required for this specification model with an almost negligible learning curve.

Breker Verification Systems Unleashes the SystemUVM Initiative to Empower UVM Engineering

Enhances Bug Hunting by Simplifying Specification Model Composition for Test Content Synthesis in Existing UVM Environments

SAN JOSE, CALIF. –– February 28, 2022 –– Breker Verification Systems used the opening of DVCon U.S. today to unveil SystemUVM™, a framework designed to simplify specification model composition for test content synthesis with a UVM/SystemVerilog syntactic and semantic approach familiar to universal verification methodology (UVM) engineers.

Developed in partnership with leading semiconductor companies, Breker’s SystemUVM’s UVM-style specification model drives test content synthesis, leveraging artificial intelligence (AI) planning algorithms for deep sequential bug hunting in existing UVM environments.

A coverage-driven approach simplifies test composition and employs up-front randomization for efficient simulation and accelerated emulation. It enhances test content reuse through configurable scenario libraries and portability for system-on-chip (SoC) integration verification and beyond.

For more information go to: www.brekersystems.com/SystemUVM

The Breker Approach

“UVM is an effective standard for block-level verification,” remarks David Kelf, Breker’s CEO. “As blocks and subsystems get larger and more complicated, composing test content for the UVM environment becomes more difficult and harder to scale. By leveraging synthesis for test content generation, a 5X improvement for larger components and multi-IP subsystems is common in composition time combined with significant coverage increases. SystemUVM makes this easily accessible for verification specialists with a minimal learning curve, dramatically changing the nature of functional verification.”

Breker’s SystemUVM layers UVM class libraries on to Accellera’s Portable Stimulus Standard (PSS) to provide the look and feel of SystemVerilog/UVM and its procedural use model. Models can be composed rapidly, efficiently reused and easily understood and maintained through UVM’s register access level (RAL), a library of common verification functions and abstract “path constraints.”

SystemUVM code offers an alternative to generic PSS while still being built on the industry standard, specifically targeting the needs of UVM engineers and recognizable to them, unleashing the power of PSS Test Content Synthesis tools, such as Breker’s TrekUVM™ and TrekSoC™ products.

SystemUVM-based Test Suite Synthesis allows the simplified generation of self-checking test content from a single abstract model complete with high-level path constraints for manageable code. Synthesis AI planning algorithms allow for specification state-space exploration, uncovering complex corner-cases that lead to potential complex bugs.

The coverage-driven nature of the process eliminates the need for coverage models and post-execution coverage analysis that results in test respins. With test randomization performed before execution, simulation is accelerated, and emulation can be used without an integrated testbench simulator, which increases its performance. The tests can also be reused in system verification via the Synthesizable VerificationOS layer without any change or disruption to the UVM testbench.

Availability and Pricing

SystemUVM is available today and is included in Breker’s Test Suite Synthesis product line. Pricing is available upon request. For more information, visit the Breker website or email info@brekersystems.com.

Breker at DVCon U.S.

DVCon’s tutorial “PSS In The Real World” opens this year’s virtual conference at 9 a.m. P.S.T., showcasing the power and flexibility of Accellera’s Portable Stimulus Standard by highlighting several real-world examples. Adnan Hamid, Breker’s executive president and CTO, is a speaker.

“In-emulator UVM++ Randomized Testbenches for High Performance Functional Verification,” a Breker-sponsored workshop also on Monday at 11:30 a.m. P.S.T., attendees will learn proven, practical methods to verify complex blocks, SoCs and sub-systems with a high degree of quality.

“The Meeting of the SoC Verification Hidden Dragons,” a panel organized by Breker and featuring Hamid will address the gap in semiconductor verification between block functional verification and system SoC validation. The panel will be held Wednesday, March 2, at 8:30 a.m. P.S.T.

About Breker Verification Systems

Breker Verification Systems is a leading provider of verification synthesis solutions that leverage SystemUVM, C++ and Portable Stimulus, a standard means to specify reusable verification intent. It is the first company to introduce graph-based verification and the synthesis of high-coverage test sets based on AI planning algorithms. Breker’s Test Suite Synthesis and TrekApp library allows the automated generation of high-coverage, powerful test cases for deployment into a variety of UVM, SoC and Post-Silicon verification environments. Case studies that feature Altera (now Intel), Analog Devices, Broadcom, IBM, Huawei and other companies leveraging Breker’s solutions are available on the Breker website. Breker is privately held and works with leading semiconductor companies worldwide.

Engage with Breker at:

Website: www.brekersystems.com

Twitter: @BrekerSystems

LinkedIn: https://www.linkedin.com/company/breker-verification-systems/

Facebook: https://www.facebook.com/BrekerSystems/

Also read:

Breker Attacks System Coherency Verification

Breker Tips a Hat to Formal Graphs in PSS Security Verification

Verification, RISC-V and Extensibility

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.