If you are interested in gaining a deeper understanding of the many ways you can leverage the Universal Verification Methodology (UVM), Breker Verification Systems has gone to a lot of effort to put that information at your fingertips.

If you are interested in gaining a deeper understanding of the many ways you can leverage the Universal Verification Methodology (UVM), Breker Verification Systems has gone to a lot of effort to put that information at your fingertips.

A technical subcommittee of Accellera voted to establish the UVM in December 2009. UVM was based on the Open Verification Methodology (OVM-2.1.1), a verification methodology that had been developed jointly in 2007 by Cadence Design Systems and Mentor Graphics. In February 2011, Accellera (a non-profit organization) formally approved a Reference Guide, a SystemVerilog class library, and a User Guide. UVM was, to a large part, based on the eRM (e Reuse Methodology) for the e Verification Language developed by Verisity Design in 2001. Accellera was likewise was based on a merger of previous standards organizations. Most standards are adopted after the fact by a dominant format already in use; standard organization share that trait as well. Accellera’s stated mission is to provide a platform in which the electronics industry can collaborate to innovate and deliver global standards that improve design and verification productivity for electronics products. And they have been at it for a while. If you have been to a DVCon event, that is run by Accellera.

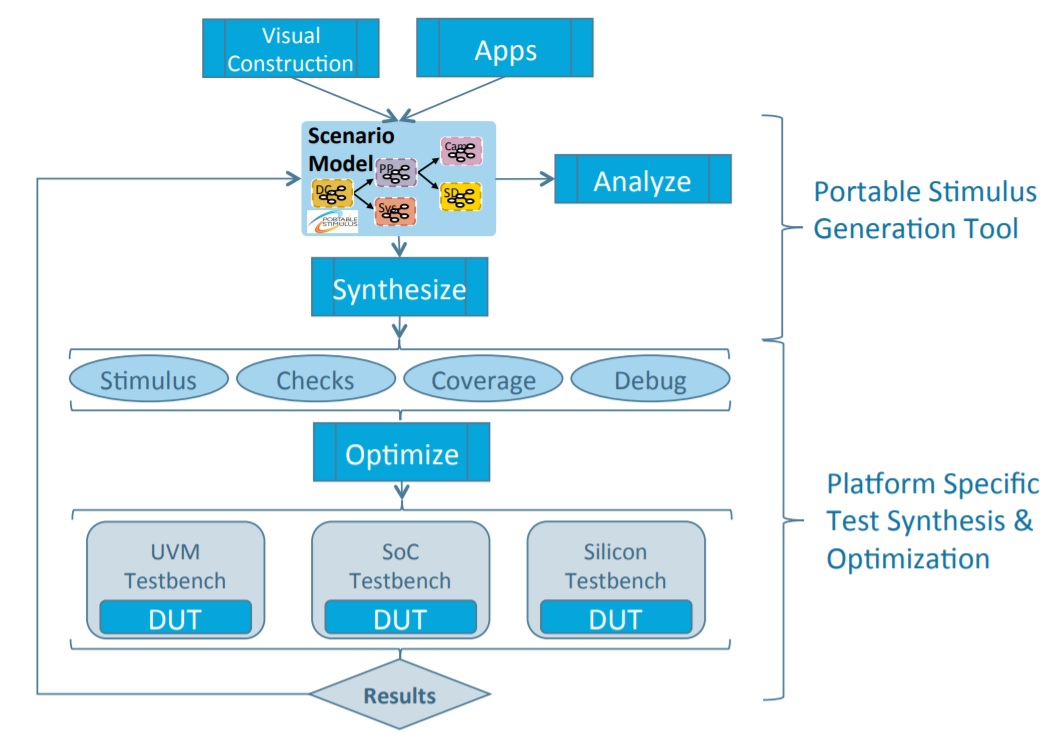

The Universal Verification Methodology (UVM) has proven to be highly effective in establishing common testbench coding methods, enabling reuse and improving the comprehension of tests. However, the methodology still has limitations that particularly impact complex block verification. The Accellera Portable Stimulus Standard (PSS) allows for many of these limitations to be eliminated, while still leveraging existing test benches, thereby not wasting legacy effort. PSS, through the Breker tools, enables a white-‐box approach to test authoring, allows complex multi-‐threaded, synchronized sequences to be generated from single scenarios, automatically provides scoreboard checks and coverage models, and generally improves test reuse and verification use models. The paper they have developed demonstrates how PSS may be leveraged in UVM environments to realize these and other advantages.

This thorough 24-page white paper will be given to attendees for Breker’s upcoming webinar, Eliminating Hybrid Verification Barriers Through Test Suite Synthesis. This webinar is the second the SemiWiki Webinar Series will be held at 10:00 am (PDT) on August 24, 2019. The primary speaker will be Aileen Honess. Aileen has more than 20 years of experience teaching, mentoring, and leading hardware verification projects across a variety of disciplines, companies, and continents. She is an expert in UVM and has recently been assisting those who are modernizing their verification methodology by adopting portable stimulus and portable specifications. To register for the event, click here, and be sure to register using your work email address.

As a special bonus, Breker intends to also give attendees a new white paper that is still in development. The working title for that white paper is ‘Finally, Thorough SoC Verification – Leveraging PSS Test Suite Synthesis for High-Coverage SoC Testing.’ This paper takes a deep dive into many of the topics that will be discussed at the webinar, so sign-up today.

About Breker Verification Systems

Breker Verification Systems is the leading provider of Portable Stimulus solutions, a standard means to specify verification intent and behaviors reusable across target platforms. It is the first company to introduce graph-based verification and the synthesis of powerful test sets from abstract scenario models. Its Portable Stimulus suite of tools is Graph-based to make complex scenarios comprehensible, Portable, eliminating test redundancy across the verification process, and Shareable to foster team communication and reuse. Breker’s Intelligent Testbench suite of tools and apps allows the synthesis of high-coverage, powerful test cases for deployment into a variety of UVM to SoC verification environments. Breker is privately held and works with leading semiconductor companies worldwide. Visit www.brekersystems.com to learn more.

Also Read

WEBINAR: Eliminating Hybrid Verification Barriers Through Test Suite Synthesis

Verification 3.0 Holds it First Innovation Summit

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.