Motion sensors are also commonly applied in a broad range of consumer products, including smartphones, wearable devices, game controllers and sports watches, with applications ranging from screen orientation to indoor navigation. If you desire to build an Inertial Measurement Unit (IMU) to efficiently compute 3D orientation,… Read More

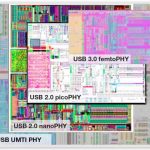

USB 3.0 IP on FinFET may stop port pinching

Sometimes a standard is a victim of its own success, at least for a while as the economics catch up to the technology. When a standard like USB 3.0 is announced, with a substantial performance increase over USB 2.0, some of the use cases come on board right away. Others, where vendors enjoy a decent ROI with good-enough performance,… Read More

How to Trim Automotive Sensor?

The electronic content in automotive is exploding, the market for automotive electronics systems is expected to grow from $170 billion in 2011 to $266 billion by 2016 (Strategy Analytics). When you seat in a brand new car, you immediately see the difference with a ten or even five years old vehicle, as you can exercise MP3 music readers,… Read More

ARC EM DSP supports Always-on Devices

The ARC EM family is the low-power, embedded and low footprint processor part of the larger ARC processor. To target the ultra low-power markets like wearable and IoT, Synopsys has added DSP capabilities to EM5D and EM7D. To be specific, these cores are optimized for ultra low-power control and DSP, thanks to:

- Energy-efficient

Selecting the Right Standard Cell & Memory for 28HPM DSP core: real case with CEVA XC4210

Listening to a webinar at your desk, in front of a PC screen will never replace a live presentation, but the lesson learned to time spent ratio can be incredibly higher than when traveling to a conference to listen several presentation. If you are interested by the approach taken by a complex DSP design team to overcome the various … Read More

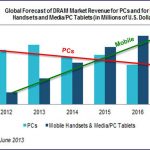

Welcome, LPDDR4!

Thanks to memory controller expert Marc Greenberg, Marketing Director for DDRn Controller IP with Synopsys, for this post “Qualcomm announces first application processor with LPDDR4 capability”. According with Marc, this Application Processor, the Snapdragon 810, is “the first product that I’m aware of that will use LPDDR4… Read More

Bye-Bye DDRn Protocol?

In fact, this assertion is provocative, as the DDR4 protocol standard has just been released by JEDEC… after 10 years discussion around the protocol features. Yes, the first discussions about DDR4 have started ten years ago! Will DDR4 be used in the industry? The answer is certainly yes, and DDR4 will most probably be used for years.… Read More

Book review: “shift left” with virtual prototypes

Shipping a product with complete software support at official release is a lot more difficult than it sounds. Inevitably, there is less than enough hardware to go around, and what little there is has to fill the needs of hardware designers, test and certification engineers, software development teams, systems integration teams,… Read More

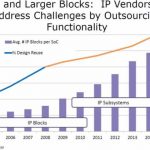

Does Multiprotocol-PHY IP really boost TTM?

I have often written in Semiwiki about high speed PHY IP supporting Interface protocols (see for example this blog), the SoC cornerstone, almost as crucial as CPU, GPU or SDRAM Memory Controller. When you architect a SoC, you first select CPU(s) and/or GPU(s) to support the system basic functionality (Processor for Mobile application,… Read More

6 reasons Synopsys covets C/C++ static analysis

By now, you’ve probably seen the news on Synopsys acquiring Coverity, and a few thoughts from our own Paul McLellan and Daniel Payne in commentary, who I respect deeply – and I’m guessing there are many like them out there in the EDA community scratching their heads a little or a lot at this. I’m not from corporate, but I am here… Read More