You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 178

[name] => IP

[slug] => ip

[term_group] => 0

[term_taxonomy_id] => 178

[taxonomy] => category

[description] => Semiconductor Intellectual Property

[parent] => 0

[count] => 1993

[filter] => raw

[cat_ID] => 178

[category_count] => 1993

[category_description] => Semiconductor Intellectual Property

[cat_name] => IP

[category_nicename] => ip

[category_parent] => 0

[is_post] =>

)

Last-level cache seemed to me like one of those, yeah I get it, but sort of obscure technical corners that only uber-geek cache specialists would care about. Then I stumbled on an AnandTech review on the iPhone 11 Pro and Max and started to understand that this contributes to more than just engineering satisfaction.

Caching

A brief… Read More

Good news is good to hear, particularly these days! The behavior of the Design IP market in 2019 is extremely positive, when the semiconductor market has seen a decline worst than in 2009 (economy crisis) or 2001 (internet bubble collapse). Analysis this 5.2% growth in detail will help to understand the future of the IP market, as… Read More

Word on the virtual street is that Wave Computing is closing down. The company has reportedly let all employees go and will file for Chapter 11. As one of the many promising new companies in the field of AI, Wave Computing was founded in 2008 with the mission “to revolutionize deep learning with real-time AI solutions that scale from… Read More

TinyML is kind of a whimsical term. It turns out to be a label for a very serious and large segment of AI and machine learning – the deployment of machine learning on actual end user devices (the extreme edge) at very low power. There’s even an industry group focused on the topic. I had the opportunity to preview a compelling webinar about… Read More

Introducing the SiFive Connect Webinar Series –A Platform Designed for Continued Engagement with the Global Hardware and Software Community Developing RISC-V Based Semiconductor Solutions

After hosting the SiFive Tech Symposiums in a record 52 cities in 2019, it became amply evident that the RISC-V revolution has reached… Read More

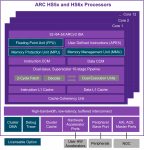

Synopsys issued a press release this morning that has some important news – Synopsys Introduces New 64-bit ARC Processor IP Delivering Up to 3x Performance Increase for High-End Embedded Applications. At first glance, one could assume this is just an announcement for some new additions to the popular ARC processor family. While… Read More

As more security related capabilities are added in hardware it is changing the effort required to ensure that SoCs are not prone to attack. Hardware has the initial appeal of creating physical barriers to attack, yet it presents its own difficulties. For one thing, a flaw in a hardware security feature is much harder to fix in the … Read More

I recently had the opportunity to attend a SemiWiki webinar entitled “Chip-to-Chip Communication for Enterprise and Cloud”. The webinar was presented by SiFive and explored chip-to-chip communication strategies for a variety of applications. In the first part of the webinar, Ketan Mehta, director of SoC IP product marketing… Read More

I got a chance to chat with Richard Solomon at Synopsys recently about a very real threat for all of us and what Synopsys is doing about it. No, the topic isn’t the Coronavirus, it’s one that has been around a lot longer and will continue to be a very real threat – data and interconnect security.

First, a bit about Richard. He is the technical… Read More

It is predicted that by 2030 energy consumption attributable to data centers will make up a staggering 8% of the world’s total usage!

As we move in to 2020 it’s clear that every sector of industry, including the semiconductor industry, will have a responsibility to address growing environmental concerns. We should be aware that… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era