You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 106

[name] => FPGA

[slug] => fpga

[term_group] => 0

[term_taxonomy_id] => 106

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 343

[filter] => raw

[cat_ID] => 106

[category_count] => 343

[category_description] =>

[cat_name] => FPGA

[category_nicename] => fpga

[category_parent] => 0

[is_post] =>

)

Vince Hu of Altera presented us her at the GlobalPress Electronics Summit on their process roadmap. Since just a month or two ago they announced that Intel would be their foundry at 14nm, everyone wanted to get a better idea of what was really going on.

At 28nm, Altera use 2 processes, TSMC 28HP (for high end Stratix-5 devices) and TSMC… Read More

Ivo Bolsens, the CTO of Xilinx, is giving the opening keynote at the Electronic Design Process Symposium (EDPS) in Monterey on Thursday and Friday this coming week. The title of his keynote is The All Programmable SoC – At the Heart of Next Generation Embedded Systems. He covers a lot of ground but the core of his presentation… Read More

The Electronic Design Process Symposium (EDPS) is April 18 & 19 in Monterey. The workshop style Symposium is in its 20[SUP]th[/SUP] year. The first session is titled “ESL & Platforms”, which immediately follows the opening Keynote address by Ivo Bolsens, CTO of Xilinx.

In his keynote presentation Ivo will present how… Read More

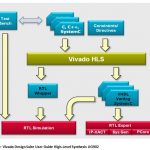

It was spring 2010 and I was asked to attend an HLS (High Level Synthesis) meeting. To be honest I cringed, after my bad relationship with Accel DSP and broken promises my heart was all walled up and needed counseling. But my management had a way of making me an offer I could not refuse, like keeping my job. So reluctantly I went. Does your… Read More

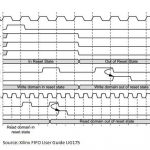

When I was not messing around with FPGA Research and Development, or Algorithms, I was often called into the lab or field and presented this type of scenario… Most of the time, the fix was the same…

At least a few times a year, I’d get the call. Sometimes a panic in the voice, or sometimes defeat. And who wouldn’t be defeated? After… Read More

Given the compressed time between 20nm and 16nm, twelve months versus the industry average twenty four months, it is time to start talking about 10nm, absolutely. Next Tuesday is the 19th annual TSMC Technology Symposium keynoted of course by the Chairman, Dr. Morris Chang.

Join the 2013 TSMC Technology Symposium. Get the latest… Read More

RTDA at Alteraby Paul McLellan on 03-12-2013 at 8:05 pmCategories: EDA, FPGA

I talked to Yaron Kretchmer of Altera to find out how they are using RTDA’s products. I believe that Altera are the oldest customer of RTDA, dating back over 15 years, originally used by the operations team around the test floor before propagating out in the EDA and software worlds more recently.

Altera use two RTDA tools, LicenceMonitor… Read More

The announcement today that Intel will be a Foundry for Altera at 14nm is a significant turning point for the Semiconductor Industry and Intel’s Foundry fortunes of which the full ramifications are not likely to be understood by analysts. As a long time follower of Intel and a former co-founder of an FPGA startup (Cswitch), it has… Read More

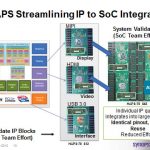

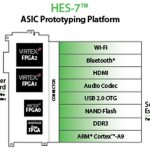

We’ve been talking about the different technologies for FPGA-based SoC prototyping a lot here in SemiWiki. On the surface, the recent stories all start off pretty much the same: big box, Xilinx Virtex-7, wanna go fast and see more of what’s going on in the design. This is not another one of those stories. I recently sat down with Mick… Read More

Roaming around the hall at ARM TechCon 2012 left me with eight things of note, but one of the larger ideas showing up everywhere is the Xilinx Zynq. Designers are enthralled with the idea of a dual-core ARM Cortex-A9 closely coupled with programmable logic.… Read More

Solving the EDA tool fragmentation crisis