You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 89

[name] => FinFET

[slug] => finfet

[term_group] => 0

[term_taxonomy_id] => 89

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 231

[filter] => raw

[cat_ID] => 89

[category_count] => 231

[category_description] =>

[cat_name] => FinFET

[category_nicename] => finfet

[category_parent] => 0

[is_post] =>

)

We all know IP is critical for advanced ASIC design. Well-designed and carefully tested IP blocks and subsystems are the lifeblood of any advanced chip project. Those IP suppliers who can measure up to the need, especially at advanced process nodes, will do well, absolutely.

It is interesting to note that eSilicon now has a very … Read More

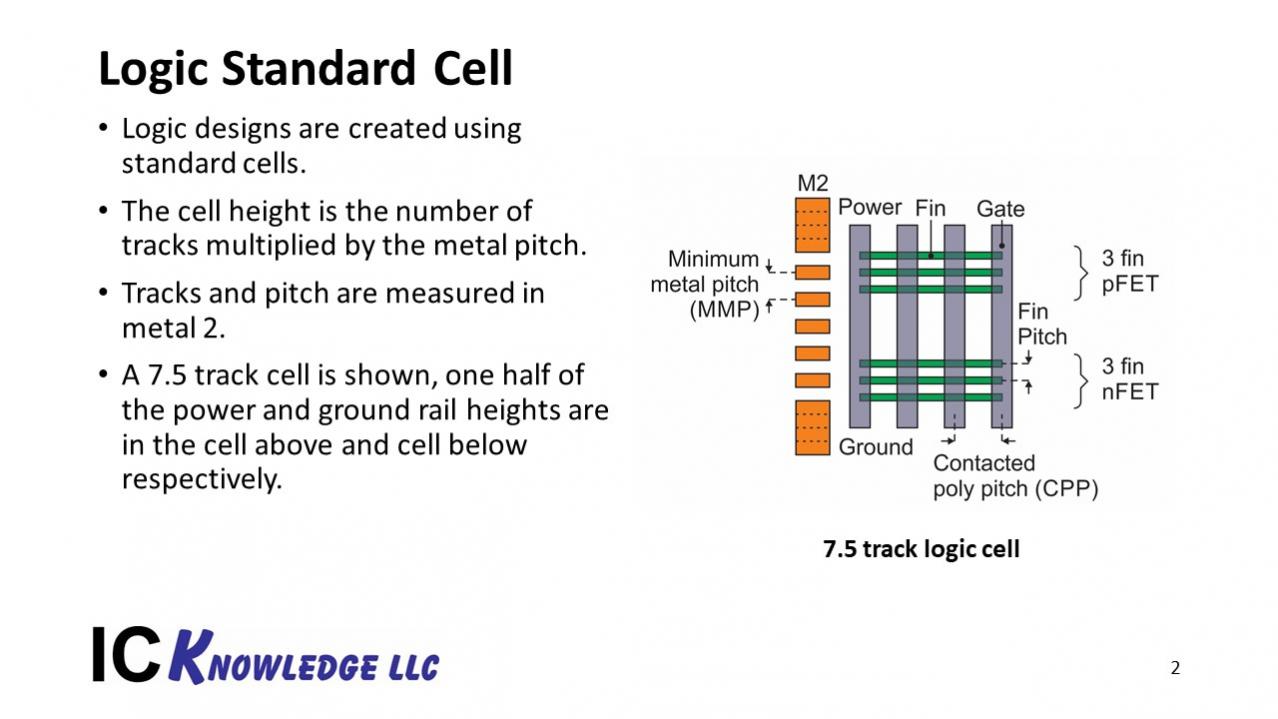

There has been a lot of new information available about the leading-edge logic processes lately. Papers from IEDM in December 2017, VLSIT this month, the TSMC and Samsung Foundry forums, etc. have all filled in a lot of information. In this article I will summarize what is currently known.… Read More

I’m not going to be at DAC this year because I scheduled a fishing trip at the end of June, assuming the show would stay true to form as an early/mid-June event. Still, having to endure salmon and halibut fishing in Alaska rather than slogging around Moscone Center, I can’t pretend to be too disappointed; I’ll be thinking of you all 😎.… Read More

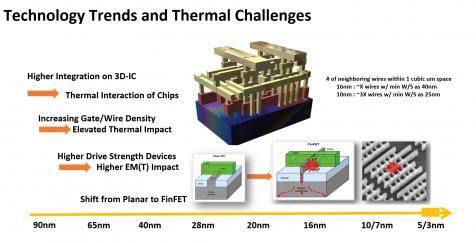

Thermal considerations have always been a concern in electronic systems but to a large extent these could be relatively well partitioned from other concerns. Within a die you analyze for mean and peak temperatures and mitigate with package heat-sinks, options to de-rate the clock, or a variety of other methods. At the system level… Read More

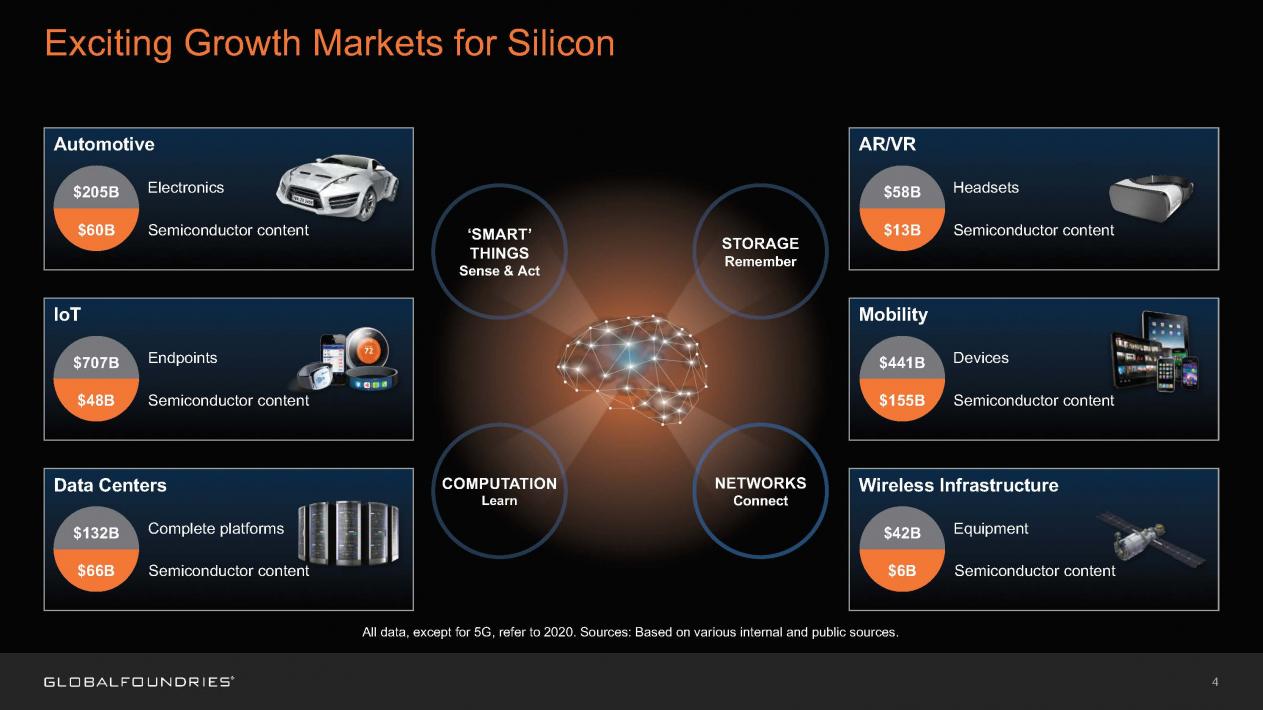

I talked to John Lee (GM of the ANSYS Semiconductor BU) recently about his views on market trends and the ANSYS big-picture theme for DAC 2018. He set the stage by saying he really liked Wally’s view on trends (see my blog on Wally’s keynote at U2U). John said these confirm what he is seeing – a trend to specialization, some around… Read More

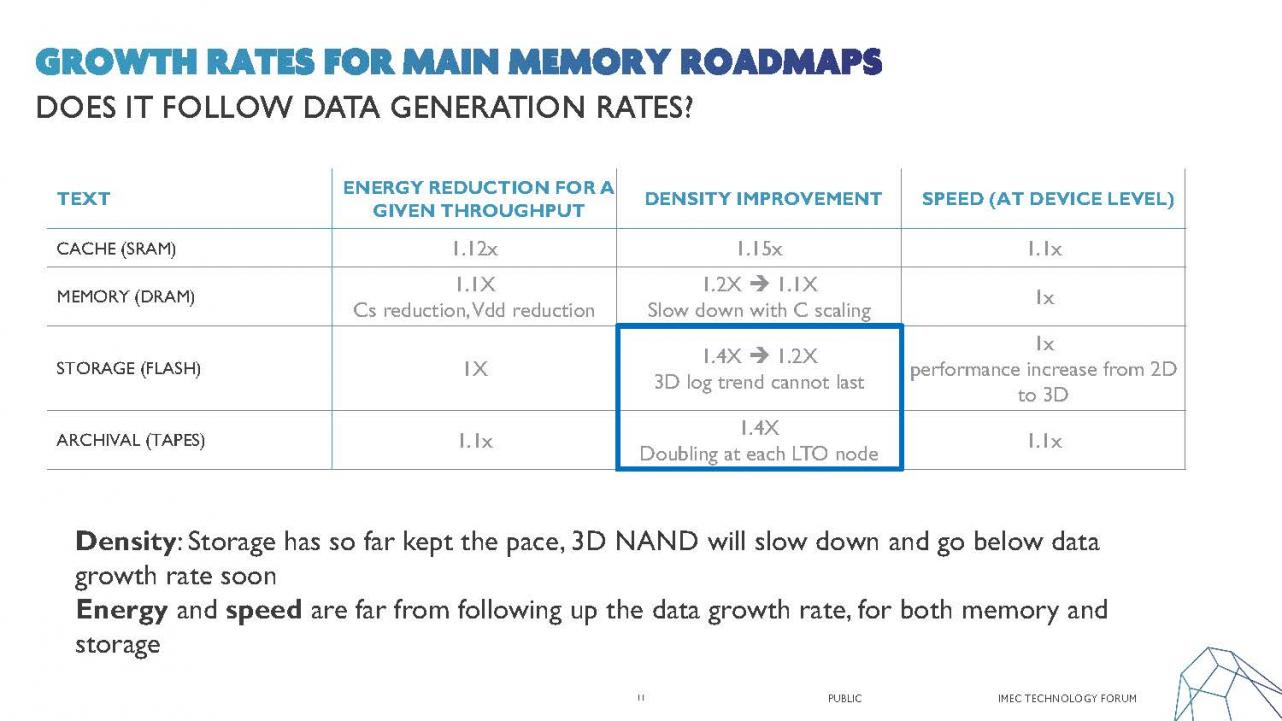

At the Imec technology forum in Belgium Gouri Sankar Kar and Arnaud Furnemont presented memory and storage perspectives and I also got to interview Arnaud. Arnaud leads overall memory development at Imec and personally leads NAND and DNA research.

Memory research is focused on power, energy, speed and cost with energy and throughput… Read More

The imec technology forum was held in Belgium last week. At the forum I had a chance to sit down with Gary Patton the CTO of GLOBALFOUNDRIES (GF) for an interview and he also presented “Enabling Connected Intelligence – Technology innovation: Enablers for an intelligent future” at the forum. In this article … Read More

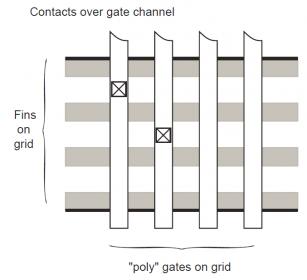

Samsung Foundry recently held their annual technology forum in Santa Clara CA. The forum consisted of: presentations on advanced and mainstream process technology roadmaps; the IP readiness for those technology nodes; a review of several unique package offerings; and, an informal panel discussion with IP designers and EDA… Read More

Will we see DDR5 memory (device) and memory controller (IP) in the near future? According with Cadence who has released the first test chip in the industry integrating DDR5 memory controller IP, fabricated in TSMC’s 7nm process and achieving a 4400 megatransfers per second (MT/sec) data rate, the answer is clearly YES !

Let’s come… Read More

It was 1988 when I got into SPICE (Simulation Program with Integrated Circuit Emphasis)while I was characterizing a 1.5 μm Standard cell library developed by students at my Alma-Mata Furtwangen University in Germany. My professor Dr. Nielinger was not only my advisor he also wrote the first SPICE bible in German language. At that… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center