The second panel is about system coverage and big data. Coverage metrics have been used to gauge the quality of verification efforts during development. At system level, there are still no standardized metrics to measure full coverage. The emergence of PSS, better formal verification, enhanced emulation and prototyping techniques… Read More

EDA and Semiconductor — Is There Growth In The Ecosystem?

The semiconductor industry has gone through several major transitions driven by different dynamics such as shift in business models (fab-centric to fab-less), product segmentation (system design house, IP developers) and end market applications (PC to cloud; and recently, to both automotive and Internet of Things — IOT’s,… Read More

Webinar: Bottlenecks be Gone – Automated Performance Verification with Synopsys

Performance verification is among the most challenging of objectives in any SoC verification plan. It’s difficult to start effectively until quite late in the development cycle, at which point you don’t have a lot of time left to develop extensive performance-oriented testbenches. So many teams adapt functional tests to this… Read More

Data Security – Why It Might Matter to Design and EDA

According to the Economist, “The world’s most valuable resource is no longer oil, but data”. Is this the case?Data is the by-product ofmany aspects of recent technology dynamics and is becoming the currency of today’s digital economy. All categories in Gartner’s Top10 Strategic Technology Trends for 2018 (Figure… Read More

Unexpected Help for Simulation from Machine Learning

I attend a lot of events on machine learning and write about it regularly. However, I learned some exciting new information about machine learning in a very surprising place recently. Every year for the last few years I have attended the HSPICE SIG dinner hosted by Synopsys in Santa Clara. This event starts with a vendor fair featuring… Read More

More Than Your Average IP Development Kit

When I think of an IP development kit, I imagine software plus a hardware model I can run on a prototyper or, closer to the kits offered by semi companies, software plus a board hosting an FPGA implementation of the IP along with DDR memory, flash and a variety of interfaces. These approaches work well for IP providers because hardware… Read More

Machine Learning And Design Into 2018 – A Quick Recap

How could we differentiate between deep learning and machine learning as there are many ways of describing them? A simple definition of these software terms can be found here. Let’s look into Artificial Intelligence (AI), which was coined back in 1956. The term AI can be defined as human intelligence exhibited by machines.… Read More

In-System Automotive Test

I’ve been driving cars since 1975 and in the early days we had simplistic gauges for feedback like: Speed, Fuel level, Oil level, RPM. Back then when you popped the hood of a car you could see through the engine compartment onto the ground below, however with today’s cars the engine compartments are crammed with tubes,… Read More

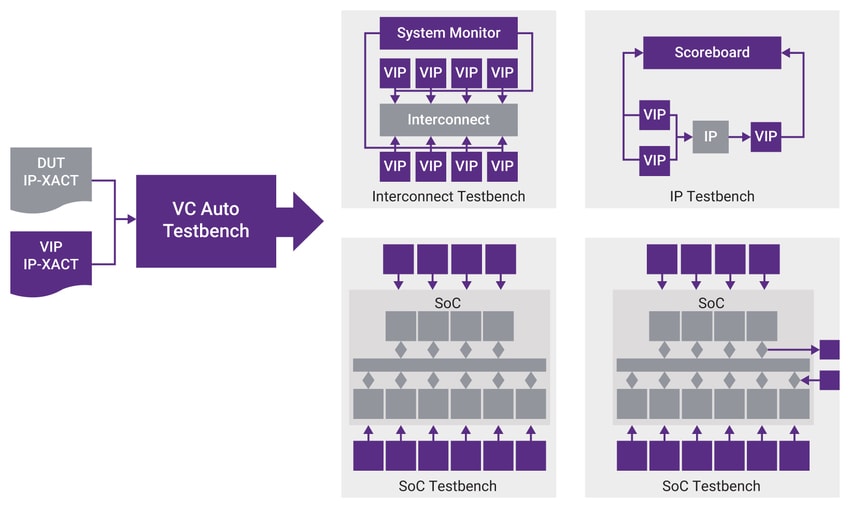

Webinar: Fast-track SoC Verification – Reduce time-to-first-test with Synopsys VC AutoTestbench

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

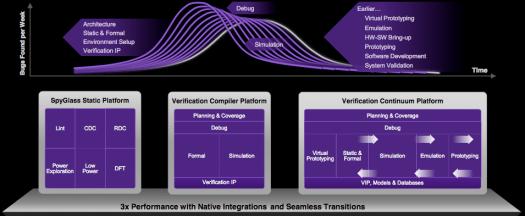

Shifting Left with Static and Formal Verification

Unless you have been living in a cave for the last several years, by now you know that “Shift Left” is a big priority in product design and delivery, and particularly in verification. Within the semiconductor industry I believe Intel coined this term as early as 2002, though it seems now to be popular throughout all forms of technology… Read More