TSMC announced today that together with ARM they have taped out the first ARM Cortex-A57 64-bit processor on TSMC’s 16nm FinFET technology. The two companies cooperated in the implementation from RTL to tape-out over six months using ARM physical IP, TSMC memory macros, and a commercial 16nm FinFET tool chain enabled by… Read More

Electronic Design Automation

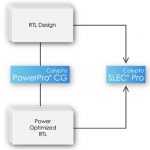

Clock Gating: Sequential Is Better

Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Trying to do sequential… Read More

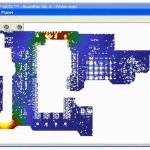

Power integrity: ground, and other fairy tales

Ground. It’s that little downward-pointing triangle that somehow works miracles on every schematic. It looks very simple until one has to tackle modern power distribution network (PDN) design on a board with high speed and high power draw components, and you soon discover ground is a complicated fairy tale with a lot of influences.… Read More

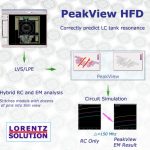

Tackling Circuit Level EM Analysis for RF, MMW and High Speed Analog Designs

Accuracy, ease of use and performance have always been paramount for electromagnetic analysis software. Historically, it has been hard to find all three of these qualities in one tool. The result is that many high speed analog and RF designers resort to using multiple, often overlapping, tools to get the job done.

Lorentz Solution… Read More

See Hogan’s Heroes at DAC 2013: The EDA Hunger Games!

Risks and Rewards of Engaging with EDA Startups:The Hunger Games!

Doing business with EDA startups comes with both risks and rewards. The Hogan’s Heroes panel at DAC 2013 features key decision makers from fabless, startup and vc firms sharing candid opinions on this risk/reward equation, and the financial and technical issues… Read More

Circuit Analysis & Debugging

In EDA we often talk about how fast a SPICE circuit simulator is, or about capacity and accuracy compared to silicon measurements. Yes, speed, capacity and accuracy are important, however when talking to actual transistor-level circuit designers you discover something quite different, most of their time is spent doing debugging,… Read More

Design Automation Conference: Go For It!

The conference program for DAC is now live here including the conference itself, keynotes, some other special tracks, the pavilion panels and more. And the must-see panel is on emulation at 4pm on Tuesday afternoon moderated by…well, that would be me so I’m a bit biased.

Mentor at TSMC Technology Symposium

TSMC will host their annual technology symposium at several locations in the U.S. on April 9th in San Jose, April 16th in Austin, and April 23rd in Boston. TSMC will discuss the market outlook, design enablement, and technology for high-speed computing, mobile communications, connectivity and storage, CIS, embedded flash, … Read More

Signal integrity: more than just SerDes analysis

When Cadence acquired Sigrity in 2012, two motives were involved: get more competitive in state of the art signal integrity analysis, and grab a foothold into the other vendor’s PCB flows in an area that is developing as a real sore spot for digital designers.

Just as the days where PCB tape-out meant actually using tape are over, … Read More

TSMC on Collaboration: JIT Ecosystem Development

Cliff Hou of TSMC gave the keynote today at SNUG on Collaborate to Innovate: a Foundry’s Perspective. Starting around 45nm the way that a foundry has to work with its ecosystem fundamentally changed. Up until then, each process generation was similar enough to the previous one, apart obviously from size, that it could be … Read More

Solving the EDA tool fragmentation crisis