Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Trying to do sequential clock gating manually is extremely difficult if at all possible, as it requires keeping track of data values over multiple cycles. But it is very attractive, especially in wide datapaths where saving unnecessary clocking can produce power savings as large as 30%. The basic idea is simple. If a register wasn’t clocked on this clock cycle, and it feeds another register on the next clock cycle then that following register does not need to be clocked on the next cycle since it already must contain the correct value. But although the basic idea is simple, getting all the details right in real world designs is not simple at all.

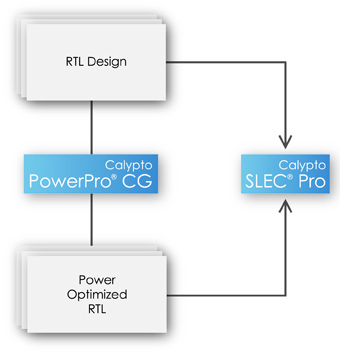

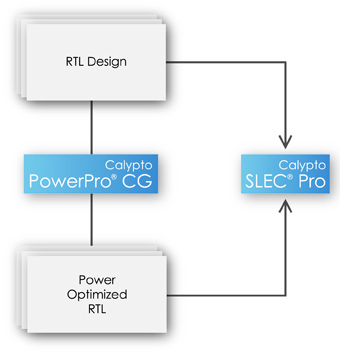

However, in addition to the challenge of correctly inferring which cycles to which registers can be gated, there is an equivalent problem which is how to verify that the inserted sequential clock-gating logic has been inserted correctly. Almost by definition, sequential clock gating changes the behavior of registers and memories and so introduces new verification challenges. Simulation is too time-consuming and is not exhaustive and ordinary formal verification often comes up short either in capability or in ease-of-use. What is required is sequential formal verification.

Next week, Rob Eccles of Calypto will present a webinar Impact of Sequential Clock Gating on Design Flow and Verification. This will cover the latest in sequential clock gating methodologies and its impact on the overall design flow,. He will also describe the latest sequential formal analysis, automated sequential clock gating, ECO and verification. Today, Rob is an AE at Calypto primarily supporting PowerPro. Prior to joining Calypto he was a design engineer and CAD engineer at AMD, Vitesse and Xilinx.

The webinar is April 9th at 10am Pacific. More details, including a link to register, are here.

Share this post via:

Solving the EDA tool fragmentation crisis