You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The Role of Clock Gatingby Steve Hoover on 11-28-2022 at 10:00 amCategories: EDA

Perhaps you’ve heard the term “clock gating” and you’re wondering how it works, or maybe you know what clock gating is and you’re wondering how to best implement it. Either way, this post is for you.

Why Power Matters

I can’t help but laugh when I watch a movie where the main characters are shrunk… Read More

When it comes to extremely power sensitive applications such as IoT and edge devices, there is literally an arsenal of power saving techniques that could be used. The tricky part is figuring out which ones to use and how to use them for maximum benefit. This is coupled with the need to not hamper device performance or functionality.… Read More

This blog is the synthesis of a white paper “New Power Management IP Solution from Dolphin Integration can dramatically increase SoC Energy Efficiency”, which can be found on Dolphin Integration web site.

The power consumption generated by complex chips was not a real issue when the system could be simply plugged in the wall to … Read More

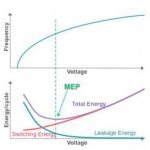

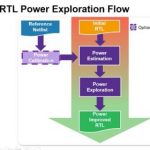

Switching translates to power. Similar to the recent slow down experienced by Moore’s Law, the constant power density (power demand per unit chip area) prescribed by Dennard scaling was no longer affordable across the technological scaling. While the contribution of leakage power component in advanced process nodes was getting… Read More

The second keynote at Mentor’s U2U this year was given by Hooman Moshar, VP of Engineering at Broadcom, on the always (these days) important topic of design for power. This is one of my favorite areas. I have, I think, a decent theoretical background in the topic, but I definitely need a periodic refresh on the ground reality from the… Read More

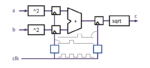

You can save a lot of power in a design by gating clocks. For much of the time in a complex multi-function design, many (often most) of the clocks are toggling registers whose input values aren’t changing. Which means that those toggles are changing nothing functionally yet they are still burning power. Why not turn off those clock… Read More

Synopsys just delivered a Webinar on using the sequential equivalence app (SEQ) in their VC Formal product to check that clock-gating didn’t mess up the functional intent of your RTL. This webinar is one in a series on VC Formal, designed to highlight the wide range of capabilities Synopsys has to offer in formal verification. They… Read More

Clock gating is arguably the mostly widely-used design method to reduce power since it is broadly applicable even when more sophisticated methods like power islands are ruled out. But this style can be fraught with hazards even for careful designers. When you start with a proven-correct logic design and add clock gating, the logic… Read More

Low power is now a goal for most digital circuit designs. This is to reduce costs for packaging, cooling, and electricity; to increase battery life; and to improve performance without overheating. I talked to the experts on physical design for ultra-low power at Mentor Graphics recently about the challenges to P&R tools and… Read More

Back in February when we shared the Sonics philosophy on the ICE-Grain Power Architecture for hardware-based SoC power management, I speculated we’d know more by DAC 2016. Sonics is hitting the road with a new live seminar coming to Silicon Valley this month and Austin during DAC – and the news is big.… Read More