Intel has been incredibly successful by designing high performance server SoC to address the data center market segment, and the chance to see the company loosing large market share is pretty low, at least in the short term. Now, if we look at the really long term, 2030 or even 2040, like did the Semiconductor Industry Association… Read More

Tag: clock gating

SoC power management a study in transition latency

Apple’s recent bout with ‘Batterygate’ highlighted just how important dynamic power management can be. Our last Sonics update looked at using their NoC to manage power islands; this time, we look at their research progress on architectural measures for power management.… Read More

Networking through Dark Silicon Power Islands

For decades, tracing back to the days of Deming, the way to tackle complex engineering problems has been the pareto chart. Charting conditions and their contribution to the problem leads to mitigation priorities.

In the case of SoC power management, the old school pareto chart said the processor core was the biggest power hog and… Read More

Power Reduction Verification Techniques Highlighted by Mentor at ARM Techcon

Power management is a perennial topic these days, and it came up in several presentations at the recent ARM Techcon in Santa Clara in mid November. The techniques covered in these talks address dynamic and static power consumption. The IEEE 1801 standard deals with specifying power design intent in Universal Power Format (UPF)… Read More

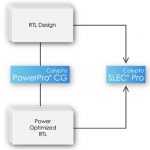

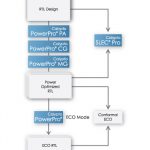

A Comprehensive Power Optimization Solution

In an electronic world driven by smaller devices packed with larger functions, power becomes a critical factor to manage. With power consumption leading to heat dissipation issues, reliability of the device can be affected, if not controlled or the device not cooled. Moreover, for mobile devices such as smartphones or tablets… Read More

How to Reduce Maximum Power at RTL Stage?

Of course that reduction has to stay throughout the design cycle up to layout implementation and fabrication. Since the advent of high density, mega functionality SoC designs at advanced nodes and battery life critical devices played by our fingertips, the gap between SoC power requirement and actual SoC power has only increased.… Read More

Smart Clock Gating for Meaningful Power Saving

Since power has acquired a prime spot in SoCs catering to smart electronics performing multiple jobs at highest speed; the semiconductor design community is hard pressed to find various avenues to reduce power consumption without affecting functionality and performance. And most of the chips are driven by multiple clocks that… Read More

Clock Gating: Sequential Is Better

Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Trying to do sequential… Read More

Watch the Clock

Clock gating is one of the most basic weapons in the armoury for reducing dynamic power on a design. All modern synthesis tools can insert clock gating cells to shut down clocking to registers when the contents of the register are not changing. The archetypal case is a register which sometimes loads a new value (when an enable signal… Read More

RTL Clock Gating Analysis Cuts Power by 20% in AMD Chip!

Approximately 25% of SemiWiki traffic originates from search engines and the key search terms are telling. Since the beginning of SemiWiki, “low power design” has been one of the top searches. This is understandable since the mobile market has been leading us down the path to fame and fortune. Clearly lowering the… Read More