The electronic content in automotive is exploding, the market for automotive electronics systems is expected to grow from $170 billion in 2011 to $266 billion by 2016 (Strategy Analytics). When you seat in a brand new car, you immediately see the difference with a ten or even five years old vehicle, as you can exercise MP3 music readers,… Read More

Electronic Design Automation

High Tech Headwinds and Project/People Management

In previous posts, we discussed the growing set of challenges and threats faced by the semiconductor industry. From saturating & stagnant systems markets to the gears starting to seize up in that engine of growth we’ve been calling Moore’s Law, chip revenues are – with the exception of memory price boosts from supply… Read More

Enterprise IP Management – A Whole New Gamut in Semiconductor Space

The world of IPs in the semiconductor landscape has completely changed the semiconductor design scenario, specifically the fabless design space. Today IPs are key components of any large semiconductor design, in the same way as auto ancillaries in auto design. It’s just the beginning, in the days to come we will see SoCs just as… Read More

End-to-end look at Synopsys ProtoCompiler

Usually, we get the incremental story in news: this new release is x percent better at this or that than the previous release, and so on. Often missing is the big picture, telling how the pieces all tie together. Synopsys took on that challenge in their latest FPGA-based prototyping webinar. … Read More

Accelerating SoC Verification Through HLS

Once upon a time there was a struggle for verification completion of semiconductor designs at gate level. Today, beyond imagination, there is a struggle to verify a design with billions of gates at the RTL level which may never complete. The designs are large SoCs with complex architectures and several constraints of area, performance,… Read More

Taking a leap forward from TCAD

We all know that Technology Computer Aided Design (TCAD) simulations are essential in developing processes for semiconductor manufacturing. From the very nature of these simulations (involving physical structure and corresponding electrical characteristics of a transistor or device), they are predominantly finite-element… Read More

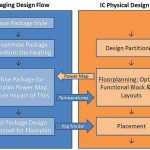

Temperature – The Fourth Aspect to Look at in SoC Design

In my career in semiconductor industry, I can recall, in the beginning there was emphasis on design completion with automation as fast as possible. The primary considerations were area and speed of completion of a semiconductor design. Today, with unprecedented increase in multiple functions on the same chip and density of the… Read More

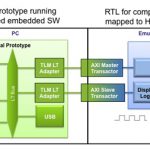

Hybrid Emulation

Hybrid emulation is when part of the system is run in the emulator and part of the system is run in a virtual prototype. Typically a model of the processor(s) is run in the virtual platform and then the rest of the design is modeled by running the RTL on the emulator. I talked to Tom Borgstrom at Synopsys about what technology they have … Read More

Power Modeling and Simulation of System Memory Subsystem

One great benefit of designing at the ESL level is the promise of power savings on the order of 40% to 70% compared to using an RTL approach. Since a typical SoC can contain a hierarchy of memory, this kind of power savings could be a critical factor in meeting PPA goals. To find out how an SoC designer could use such an ESL approach to power… Read More

Cadence Results: Good but Palladium under Price Pressure

Cadence announced their 2Q results this afternoon. I listened to the conference call.

You can read all the details of the results in the press release but the big picture is:

- Revenue $379K, net income $23M GAAP or $64M non-GAAP (8, 21c per share, beat estimates by 1c). Equivalent quarter last year was $362M so less than 5% increase)

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!