You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4457

[filter] => raw

[cat_ID] => 157

[category_count] => 4457

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Last week I sat down and talked to Bijan Kiani of Synopsys. He has marketing responsibility for design implementation products at Synopsys spanning digital, custom and analog mixed signal (AMS).

He was born in Iran and after high school he moved to the UK. He got his PhD degree from University of Edinburgh. It turns out that I was doing… Read More

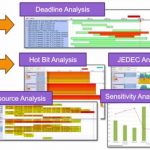

With the increase of transistors per unit area, high density interconnects and manufacturing variability at lower nodes, the electronic devices have become more vulnerable to failures. The devices that operate under extreme conditions such as automotive devices that operate at high temperatures need to be robust enough to… Read More

Almost exactly a year ago I wrote about Silicon Cloud International (SCI). Their mission is to help smaller countries that have targeted semiconductor design as a way to move up the technology ladder from low-cost manufacturing. Last year everything was in the future but SCI now have their first two centers up and running. The first,… Read More

We have been hearing about low power for a long time. Fortunately, low power chip operation has come about through a large number of innovations. Key among these is clock gating, frequency and voltage scaling, managing leakage with lower threshold voltage, HKMG, and many other techniques. But we are entering the age of ultra low… Read More

Although I knew about Crossfire’s capabilities for signing off quality of an IP before its integration into an SoC, there was much more to learn about this tool when I visited Fractal Technologies booth during this DAC. The complexity handled by this tool to qualify any type of IP for its integration into an SoC can be imagined by the… Read More

One announcement that I missed coming up to the Design Automation Conference last week was that SiCAD is hosting a portfolio of IBM’s design automation tools in the cloud. Supposedly these are priced half the cost of similar capability from Cadence, Synopsys and Mentor. So should the big three be worried? Is this an earth-shattering… Read More

Last year at #51DAC we gave away more than a thousand printed versions of our book “Fabless: The Transformation of the Semiconductor industry.” This year we gave away pens with a light and stylus. My friends at Solido Design gave away 600 pens in their booth and we gave away another 400 at our DAC reception on Wednesday night. Solido… Read More

It appears so. Why there is so much rush towards FD-SOI in recent days? Before talking about the game, let me reflect a bit on the FD-SOI technology first. The FD-SOI at 28nm claims to be the most power-efficient and lesser cost technology compared to any other technology available at that node. There are many other advantages from… Read More

The CEO Fireside Chats were my very favorite part of #52DAC. Dr. Walden Rhines, Lip-Bu Tan, and Dr. Aart de Geus are heroes of the EDA industry, absolutely. I saw all three Fireside Chats and the one word that I’m left with is INSPIRED! … Read More

In optimizing SoC design for performance, there is so much focus on how fast a CPU core is, or a GPU core, or peripherals, or even the efficiency of the chip-level interconnect. Most designers also understand selecting high performance memory at a cost sweet spot, and optimizing physical layout to clock it as fast as possible within… Read More

Solving the EDA tool fragmentation crisis