You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4457

[filter] => raw

[cat_ID] => 157

[category_count] => 4457

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

While tracking Moore’s Law has become a more expensive and difficult endeavor in the HPC design, the mobile SOC design space is also increasingly heterogeneous and complex. Strict safety guidelines such as the ISO-26262 being imposed in the automotive applications further exacerbate the situation.

Looking closer into the … Read More

The year is 1999 and I decided that is time to try something else in layout. In 1989 in Israel I was part of the biggest chip in the world, the Motorola DSP9600. In 1998 in Canada I was part of the biggest Synchronous DRAM in the world, it was time to try analog/mixed signal/RF projects.

The opportunity came from PMC Sierra who already had… Read More

During DVCon 2018 in San Jose, one topic widely covered was the necessity of describing and capturing intent. Defining our design intent up-front is crucial to the overall success of a design implementation. It is not limited to applying a process level intent, such as the use of verification intent with embedded assertions in … Read More

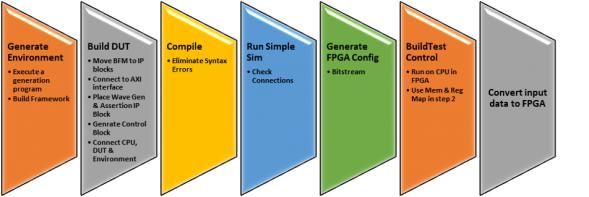

We all know the basic premise of emulation: hardware-assisted simulation running much faster than software-based simulation, with comparable accuracy for cycle-based 0/1 modeling, decently fast setup, and comparably fine-grained debug support. Pretty obvious value for running big jobs with long tests. But emulators tend… Read More

EDA CEO Outlook 2018by Daniel Nenni on 04-06-2018 at 12:00 pmCategories: EDA, Events

The EDA CEO outlook took an interesting turn last night but before I get into that I will offer a few comments about the start of the show. I attend this event every year for the content but also for the networking. It isn’t everyday you get to hang out with semiconductor industry elite and have candid conversations over food and drinks.… Read More

As verification continues to be a key ingredient in successful design implementation, new approaches have been tried to balance cost, time to results and comprehensive analysis in designs that require large patterns in some application like Image Processing. Simulation environments are well proven, and designers tend to … Read More

These failings aren’t just a cross we humans bear; they’re also a concern for chips, particularly in electrical over-stress (EOS) and aging of the circuitry. Such concerns are not new, but they are taking on new urgency given the high reliability and long lifetime expectations we have for safety-critical components in cars and… Read More

Publishing eBooks on FPGA Prototyping and Emulation really was an eye opener for me as a long time EDA and IP professional. Both markets are considered EDA in the traditional sense but they are very much in the systems business with a lot of IP. Both markets are also growing very rapidly and operate side-by-side with complimentary… Read More

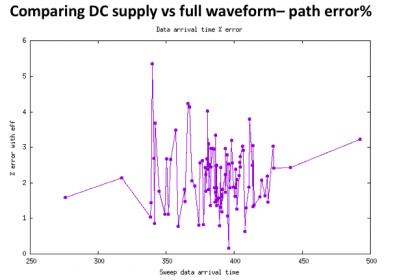

About 6 months ago, ANSYS was approached by a couple of leading mobile platform vendors/suppliers with a challenging problem. These companies were hitting target 2.5GHz performance goals on their (N10 or N7) application processors, but getting about 10% lower yield than expected, which they attributed to performance failures.… Read More

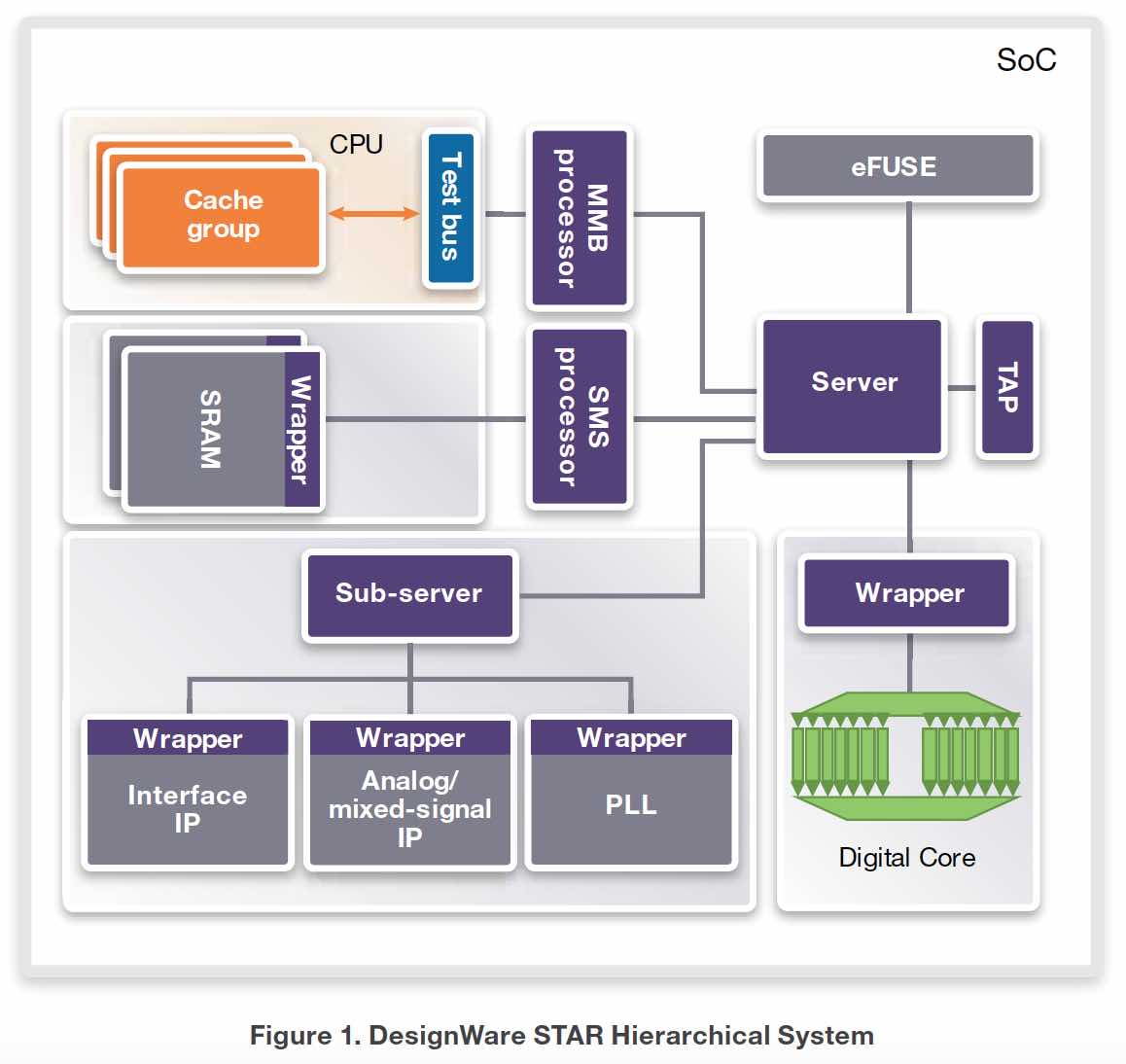

When it comes to safety, ISO 26262 is the spec that comes to mind for many people. However, there are layers of specifications that enable the level of safety required for automotive and other systems that need high reliability. For any application requiring safety, test is a critical element. A key spec for SOC test is IEEE 1500, … Read More

Solving the EDA tool fragmentation crisis