When it comes to safety, ISO 26262 is the spec that comes to mind for many people. However, there are layers of specifications that enable the level of safety required for automotive and other systems that need high reliability. For any application requiring safety, test is a critical element. A key spec for SOC test is IEEE 1500, which defines a hierarchical test structure for SOC’s that enables testing of individual blocks and circuit elements independently. With a hierarchical testing approach chip testing becomes much more efficient, and new types of test functionality can be implemented.

Coming back to ISO 26262, one of the critical aspects is testing over the life of a chip to ensure it is performing properly as it ages. ISO 26262 includes provisions for real-time testing on a continuous basis to ensure proper performance over time. And, if we are talking about things that are required for proper performance, few matter more than clock performance, process variation and memory performance. These aspects of an SOC define the foundation that all other aspects of system reliability depend on.

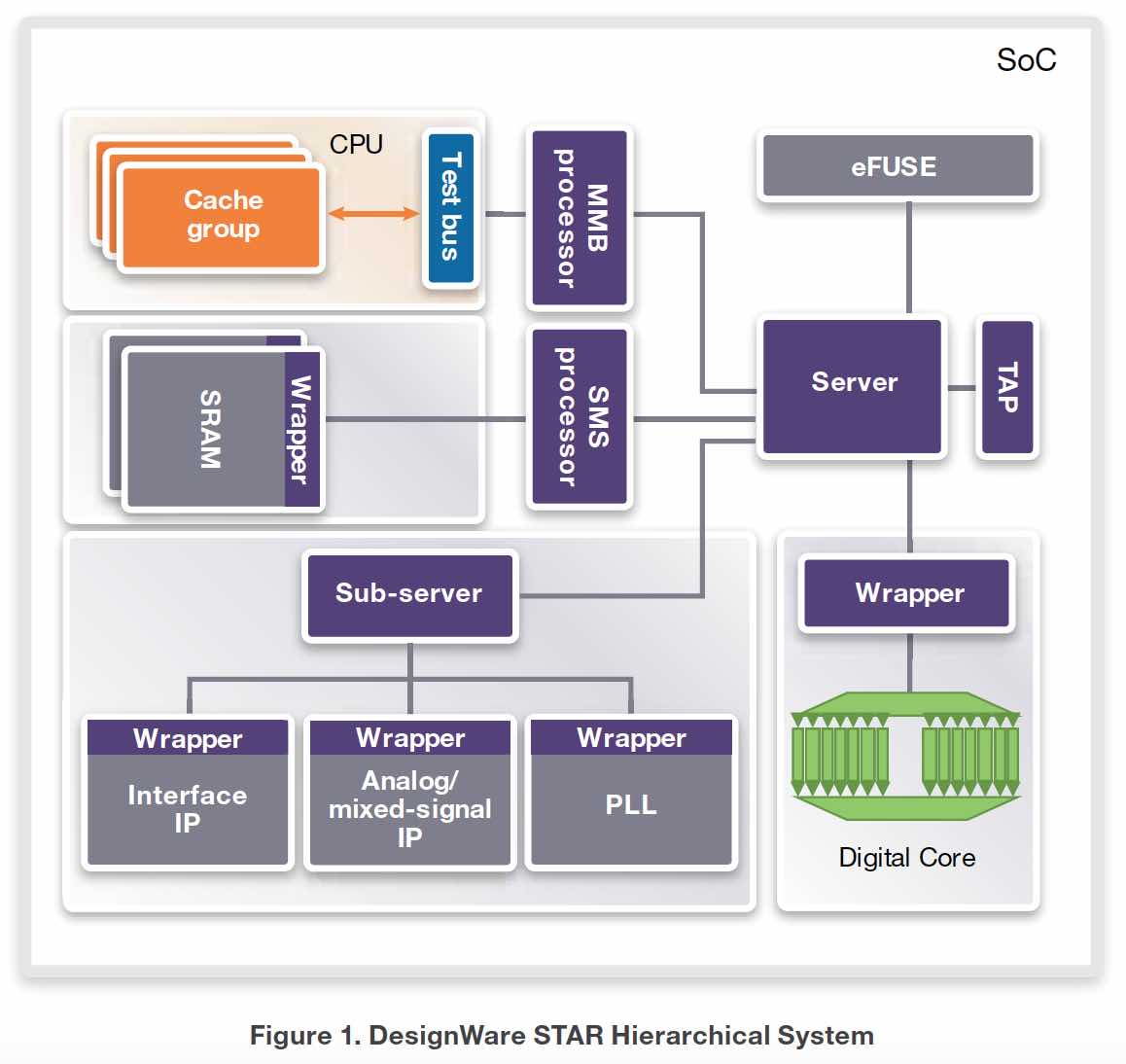

In the white paper below Synopsys references their Measurement Unit (MU) which is part of its STAR Hierarchical System for SOC test implementation. The STAR Hierarchical System offers a means of implementing comprehensive test on SOC’s. It has been certified for ISO 26262 ASIL D level applications. To refresh, ASIL D is applied to systems whose failures can lead to death or serious injury.

There is a need for a compact and efficient method to test for clock frequency and duty cycle over the life of an SOC in ASIL D systems. The MU cleverly performs these function with minimal external support. The MU is configurable to perform several different functions, with clock frequency as the only one requiring an external reference clock. Even so, the reference clock can be a low speed clock. The MU counts the internal and external clock pulses and returns the internal clock period.

The MU also has a mode which tests duty cycle for internal clocks, this time with no external reference clocks required. Synopsys has also added modes to the STAR Hierarchical System’s MU to report process variation by using it in conjunction with a ring oscillator. Once the system clock is calibrated, the MU can evaluate process variation by comparing ring oscillator frequencies. This is useful when performed in a single location to monitor the effects of aging, or across multiple locations to look at on chip variation that could jeopardize chip performance. This same mode can be used to evaluate IR drop related performance issues. The test can be performed at chip idle mode and during high activity to determine the effects of IR drop.

The MU also has an operational mode for testing memory performance. The details of this mode are explained in the white paper mentioned above. The white paper is titled On-Chip Clock and Process Monitoring Using STAR Hierarchical System’s Measurement Unit and can be found on the Synopsys website. The white paper is authored by Karen Darbinyan, ASIC Digital Design Manager at Synopsys.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.