The introduction of 5G communications support offers tremendous potential across a broad spectrum of applications (no pun intended). 5G is indeed quite encompassing, across a wide range of frequencies – the figure below illustrates the common terminology used, from low-band, mid-band (“sub 6G”), and high-band (“mmWave”)… Read More

Electronic Design Automation

Workflow Automation Applied to IP Lifecycle Management

I often blog about a specific EDA tool, or an IP block, but the way that SoC design teams approach their designs and then use tools and IP can either be a manual, ad-hoc process, or part of something that is well-documented, following a design methodology. Back in the 1980’s while at Intel our team first created a design methodology… Read More

Synopsys and Infineon prepare for expanding AI use in automotive applications

We all know that cars are using processors for many tasks, but it is easy to fail to comprehend just how many there are in a typical modern car. Browsing through the Infineon AURIX automotive processor application guide, you can start to see just how pervasive processors are. The AURIX processors are specifically designed for automotive… Read More

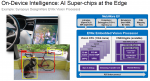

AI Hardware Summit, Report #3: Enabling On-Device Intelligence

This is the third and final blog I have written about the recent AI Hardware Summit held at the Computer History Museum in Mountain View, CA. Day 1 of the conference was more about solutions in the data center, whereas Day 2 was primarily around solutions at the Edge. This presentation from Day 2 was given by Dr. Thomas Anderson, Head,… Read More

Debugging SoCs at the RTL, Gate and SPICE Netlist Levels

Debugging an IC is never much fun because of all the file formats used, the levels of hierarchy and just the sheer design size, so when an EDA tool comes around that allows me to get my debugging done quicker, then I take notice and give it a look. I was already familiar with debugging SPICE netlists using a tool called SPICEVision Pro,… Read More

Webinar: OCV and Timing Closure Sign-off by Silvaco on Oct 10 at 10AM

The old adage that goes the one constant thing you can always count on is change, could easily be reworded for semiconductor design to say the one constant thing you can count on is variation. This is doubly true. Not only is variation, in all its forms, a constant factor in design, additionally the methods of analyzing and dealing … Read More

Webinar: Finding Your Way Through Formal Verification

Formal verification has always appeared daunting to me and I suspect to many other people also. Logic simulation feels like a “roll your sleeves up and get the job done” kind of verification, easily understood, accessible to everyone, little specialized training required. Formal methods for many years remained the domain of … Read More

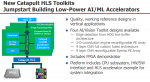

AI Hardware Summit, Report #2: Lowering Power at the Edge with HLS

I previously wrote a blog about a session from Day 1 of the AI Hardware Summit at the Computer History Museum in Mountain View, CA, held just last week. From Day 2, I want to delve into this presentation by Bryan Bowyer, Director of Engineering, Digital Design & Implementation Solutions Division at Mentor, a Siemens Business.… Read More

Virtually Verifying SSD Controllers

Solid State Drives (SSDs) are rapidly gaining popularity for storage in many applications, in gigabytes of storage in lightweight laptops to tens to hundreds of terabyte drives in datacenters. SSDs are intrinsically faster, quieter and lower-power than their hard disk-drive (HDD) equivalents, with roughly similar lifetimes,… Read More

High-Speed PHY IP for Hyperscale Data Centers

A new designation has recently entered the vernacular of the computing industry – a hyperscale data center. The adjective hyperscale implies the ability of a computing resource to scale corresponding to increased workload, to maintain an appropriate quality of service.

The traditional enterprise data center is often characterized… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era