You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The engineering team for the design and analysis of a complex system consists of a diverse set of skills — with the increasing emphasis on both high-speed interface design and multi-domain power management, a critical constituent of the team is the group of signal integrity (SI) and power integrity (PI) engineers.

The training… Read More

IP development strategy and hockeyby Tom Dillinger on 01-19-2017 at 7:00 amCategories: Analog Bits, FinFET, IP, TSMC

One of the greatest hockey players of all time, Wayne Gretzky, provided a quote that has also been applied to the business world — “I skate to where the puck will be, not to where it has been.” It strikes me that this philosophy directly applies to IP development, as well. Engineering firms providing IP must anticipate… Read More

The Year of the eFPGAby Tom Dillinger on 01-17-2017 at 12:00 pmCategories: eFPGA, Flex Logix, FPGA, IP

The start of the new year is typically a time for annual predictions. Prognostications are especially difficult in our industry, due to the increasing difficulty in Moore’s Law technology scaling and greater design complexity challenges. There is one sure prediction, however — this year will see the emergence … Read More

It’s All About the Modelsby Tom Dillinger on 01-14-2017 at 7:00 amCategories: EDA, FD-SOI, FinFET

The world-renowned statistician, Professor George Box, said, “Essentially, all models are wrong, but some are useful.” — that quote was the theme for one of the technical talks at the recent MOS-AK Workshop, held at UC-Berkeley. … Read More

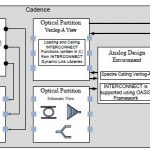

Photonics IC’s (PIC’s) are used to transmit and receive data through a (single-mode or multi-mode) optical fiber carrier, and provide the requisite electro-optical conversion for system integration. The architecture of the PIC spans the full characteristics of data transmission and reception:

Typically,… Read More

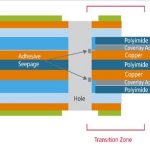

"Rigid-Flex Design is Coming"by Tom Dillinger on 10-04-2016 at 12:00 pmCategories: Cadence, EDA

Printed circuit boards that incorporate a combination of traditional PCB technology with flexible substrates, aka rigid-flex designs, have enabled an increasing variety of product designs, that leverage the unique physical form factor and lightweight options that rigid-flex technology offers. Yet, this technology requires… Read More

Recently, TSMC conducted their annual Open Innovation Platform forum meeting in San Jose. Although TSMC typically eschews a theme for the forum, David Keller, EVT TSMC North America, used a phrase in his opening remarks that served as a foundation for the rest of the meeting – “celebrate the way we collaborate”.

The forum begins… Read More

Electronic system level (ESL) modeling for system architecture exploration is rapidly gaining momentum. The simulation performance requirements for hardware/software co-design are demanding — an abstract model for SoC IP cores is required. Typically, soft IP will include a number of model configuration parameters.… Read More

Integrated wafer-level fanout (WLFO) packaging technology is emerging as a foundation for multi-die solutions. Mobile product applications require focus on both aggressive chip-to-chip interface performance, as well as the final package volume. Traditional multi-chip packages using PCB laminate substrates do not readily… Read More

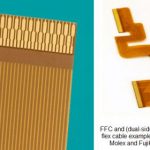

The three F’s of electronic product development are: form, fit, and function. Although the F/F/F assessment typically refers to the selection of the right component, it most definitely also refers to the selection of the proper cabling between assemblies. The requirements for cables are varied, and demanding: ability… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior