When I upgraded cars from a 1988 to 1998 Acura it seemed like my car had become much smarter with a security chip in the key, security codes in the radio and a connector for computer diagnosis, however in today’s modern auto there’s a lot more mixed-signal design content. Micronasand Synopsysgot together and hosted … Read More

Tag: webinar

SiC and Si Power Devices

ICs for consumer electronics are often battery powered, which are considered low voltage designs. On the other end of the IC spectrum are high voltage devices used in many industrial applications like: automotive, aerospace, data centers, transportation and power generation. … Read More

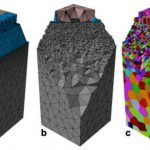

TCAD to SPICE Simulation of Power Devices

The periodic table shows that Silicon (Si) is in a column along with other elements like Carbon (C) and Germanium (Ge). With so much emphasis on Silicon, you’d think that the other semiconductor materials have been neglected a bit.

Silicon is a wonderful material and most of our consumer electronics and handheld devices … Read More

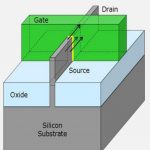

FinFET Design for Power, Noise and Reliability

IC designers have been running analysis tools for power, noise and reliability for many years now, so what is new when you start using FinFET transistors instead of planar transistors? Calvin Chow from ANSYS (Apache Design) presented on this topic earlier in the summer through a 33 minutewebinar that has been archived. There is… Read More

Improving Complex System Design

Next week Mike Jensen of Mentor will present a webinar Improving Complex System Design Reliability and Robustness. The webinar will be presented live twice and presumably available for replay soon after, as is usually the case:

- September 4th 6.00-6.45am pacific (9pm in Asia, 3pm in most of Europe)

- September 4th 10.00-10.45am

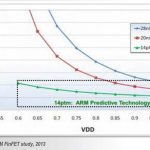

FinFETs for your Next SoC

Planar CMOS processes have been offered for decades now, and all the way down through the 28nm node it has been riding the benefits of Moore’s Law. A few years back we started hearing from Intel about TriGate (aka FinFET) starting at the 22nm node as a way to use a more 3D processing approach for transistors instead of planar CMOS.… Read More

Transaction-based Emulation

Verification has been going through a lot of changes in the last couple of years. Three technologies that used to be largely contained in their own silos have come together: simulation, emulation and virtual-platforms.

Until recently, the workhorse verification tool was simulation. Emulation had its place but limits on capacity… Read More

eSilicon and the Ten Minute Quote

One of the challenges in bringing a design into production is getting a quote that includes all the various stages of the process. The quote cycle typically takes a couple of weeks. It is also pretty wasteful. A typical design might be quoted by 3 manufacturers and so 2 out of 3 quotes are wasted expense because the design is lost to a … Read More

Making IP Reuse and SoC Integration Easier

The last graphics chip that I worked on at Intel was functionally simulated with only a tiny display size of 16×16 pixels, because that size allowed a complete regression test to be simulated overnight. Our team designed three major IP blocks: Display Processor, Graphics Processor and Bus Interface Unit. We wanted to also… Read More

Catching IC Manufacturing Defects With Slack-Based Transition Delay Testing

Test engineers are often the unsung heroes in the semiconductor world, because they have the tough job of deciding if each IC is good or bad, while taking the least amount of time on a tester and ensuring that the tests are actually finding and uncovering all manufacturing and process variation defects. Simple stuck-at fault models… Read More