Test engineers are often the unsung heroes in the semiconductor world, because they have the tough job of deciding if each IC is good or bad, while taking the least amount of time on a tester and ensuring that the tests are actually finding and uncovering all manufacturing and process variation defects. Simple stuck-at fault models are no longer sufficient to catch all of the actual defects, so to achieve the highest quality and lowest Defective Parts Per Million (DPPM) new Transition Delay (TD) patterns are being used. Extending TD testing with Slack-Based Transition Delay (SBTD) testing is a new approach for even higher defect coverage. A recent webinarpresented by Synopsys and Avago focused on this test topic.

Avago Technologies is a leading designer, developer and global supplier of a broad range of analog, digital, mixed signal and optoelectronics components and subsystems with a focus in III-V compound semiconductor design and processing.

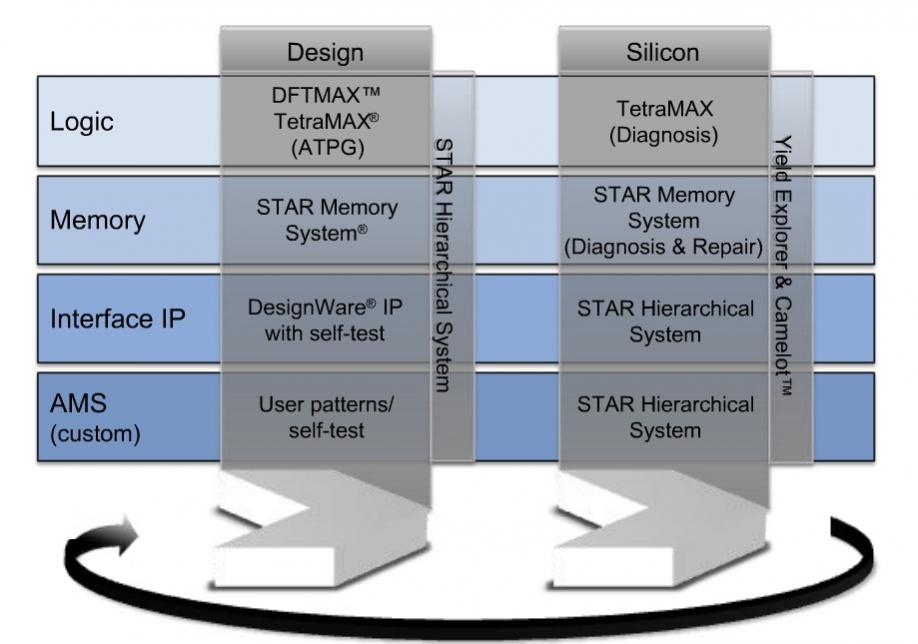

Synopsys has assembled all of their test software into two parts: Design and Silicon. Shown below are the four categories of IP used in SoCs today: Logic, Memory, Interface IP and AMS. Each IP category has test software corresponding to both design and silicon.

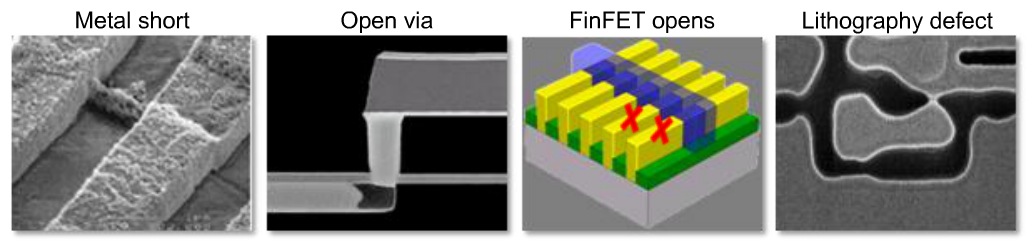

Examples of physical defects that must be detected and tested for include: Metal shorts, open vias, FinFET opens, and lithography defects.

Automatic Test Pattern Generation (ATPG) tools like TetraMAX employ different fault models and tests to target each class of possible defects:

- Stuck-at

- Static Bridge

- Dynamic Bridge

- IDDQ

- Slack-Based

- Path Delay

- Hold-Time

- Cell-Aware

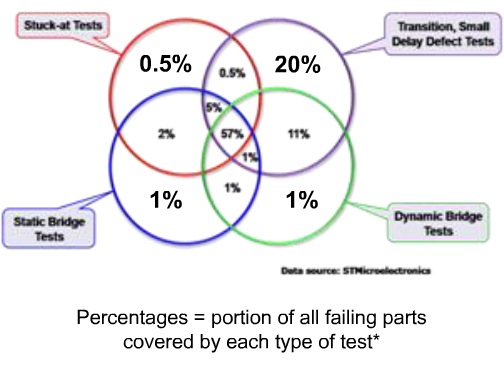

A Synopsys customer analyzed their test coverage over a specific SoC design using multiple fault models, then presented the data as a Venn diagram:

“Small Delay Defect Testing.” EDN. June 2009

Delay Defects

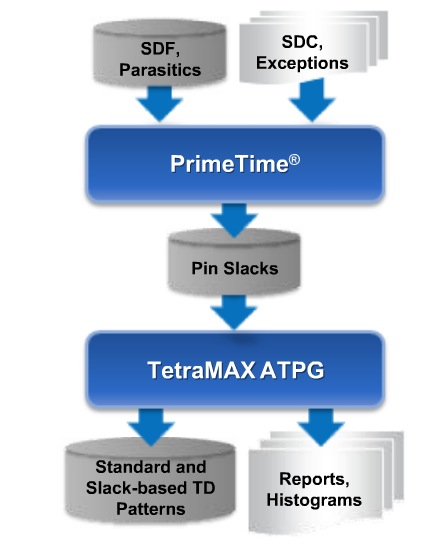

The new method to target delay defects is called slack-based transition test, and a paper was presented at ITC 2007, “Fundamentals of Timing Information for Test: How Simple Can We Get?“. To get detailed timing information into ATPG for delay defects requires a Static Timing Analysis (STA) tool, so here’s the Synopsys flow from PrimeTimeinto TetraMAX ATPG:

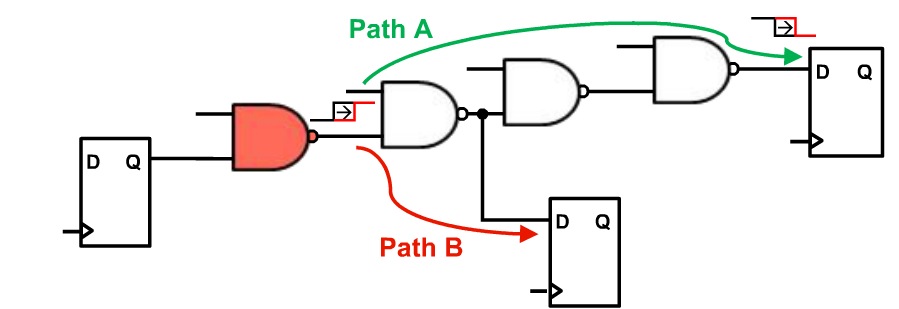

The difference between a slack-based transition path (Path A) and a standard transition delay path (Path B) are shown below:

Path A is longer with three gate delays until the next DFF, while Path B is shorter with only one gate delay until the next DFF. The longer Path A will have the minimum-slack and is tested with SBTD patterns, while the shorter Path B is detected by standard TD patterns. You really want both paths to be tested, so that requires two ATPG algorithms.

Avago Results

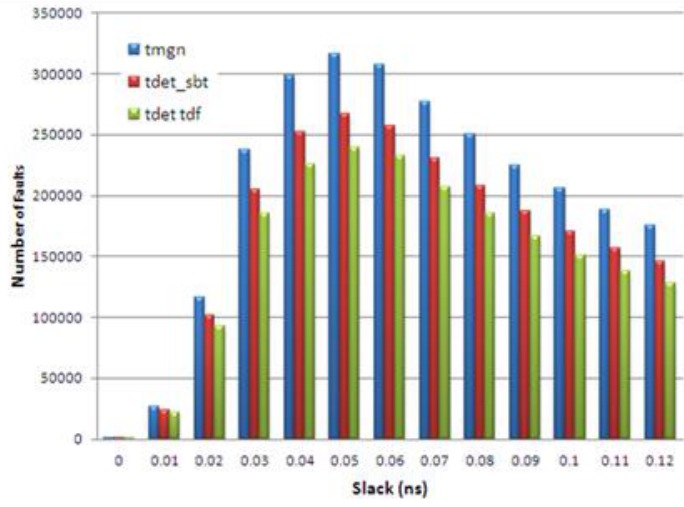

Stefano Zanatta from Avago shared his experience of achieving a target of <15 DPPM using the new slack-based transition fault testing. They were able to keep the SBTD patterns within their target of 25% of standard TD patterns. The TetraMAX tool reported the total number of faults detected as a function of Slack in three categories:

- (Blue) Targeted delay faults, distributed according to their minimum slacks

- (Red) SBTD detected faults

- (Green) Standard TD faults

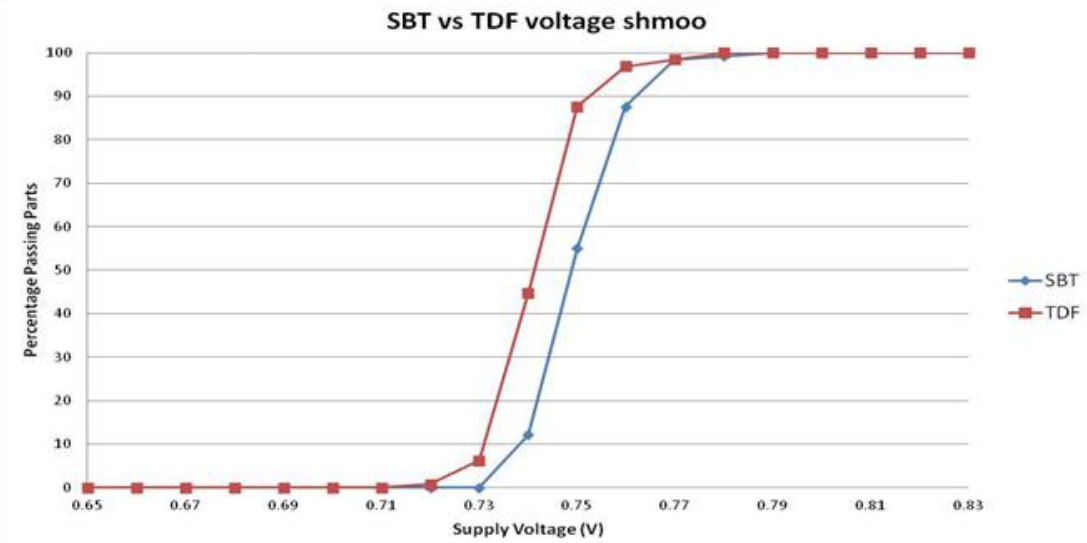

Ideally you want the Red bars to be as high as the Blue bars, so that all of the delay faults are being caught by SBTD patterns. The quality of the SBTD patterns was 84% versus TD patterns at 73% for this particular design. Another comparison of SBTD versus TD patterns was measured in silicon where the power supply voltage was shmoo plotted versus the percentage of passing parts:

Starting from the left-hand side of the plot at 0.65V none of the parts are passing, and as the supply voltage is increased then the parts begin to pass. At the 0.76V supply voltage level the TD patterns are passing 98% of the parts, while the more thorough SBTD patterns are passing 88% of the parts.

Summary

Avago has successfully added SBTD patterns in their test flow to improve DPPM levels beyond what is possible with just traditional TD patterns. The complete 36 minute webinarhas been recorded and can be viewed online after a brief registration. Chris Allsup from Synopsys has also authored a 6 page White Paper – More Effective Test: Slack-Based Transition Delay.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.