I’ve written before about eSilicon’s IP Marketplace. This is the latest in several steps to automate more and more of the interface between eSilicon and its customers: MPW quotes, production quotes, tracking orders through manufacturing, and now IP quotes. There is a phrase in software development called “eating… Read More

Tag: webinar

Benefits of Using Schematic Driven Layout

Most IC designs are developed by a team of professionals, often separated into distinct groups like front-end and back-end, logical and physical designers. Circuit designers use tools like schematic capture at the transistor-level to create a topology, then begin simulating the netlist with a SPICE simulator. Layout designers… Read More

How to Optimize for Power at RTL

Last week I was traveling in Munich attending the MunEDA User Group meetingso I missed a live webinar on the topic of optimizing for power at RTL. I finally got caught up in my email this week and had time to view this 47 minute webinar, presented by Guillaume Boilletof Atrenta. He recommended using a combination of automatic, semi-automatic… Read More

IC Place and Route for AMS Designs

High-capacity IC place and route (P&R) tools can cost $200K and more to own from the big three vendors (Cadence, Synopsys, Mentor), but what about IC designs that are primarily Big Analog and Little Digital? In the EDA world we often have multiple choices for tools, and there are affordable alternatives to place and route out… Read More

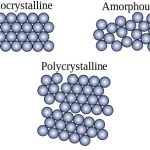

Leakage Current TCAD Calibration in a-Si TFTs

Two weeks ago I blogged about amorphous silicon and how that material is well-suited for designing TFTs. Today I’m following up after watching the archived webinarpresented by Nam-Kyun Tak of Silvaco. After clicking on that link you’ll be brought to a brief sign-up page and then can watch the archived webinar in your… Read More

NoC 101, a Sonics Webinar

One of the things that I’ve been telling the people at Sonics when they will listen is that they should do a bit more basic education on Networks on Chip (NoC). Sure, the people who actually use Sonics’s products care about deep details such as security and power management, but there is a whole host of designers who have… Read More

Getting a Quote Without Talking to a Salesman

VLSI Technology, for those of you not of a certain age, was one of the companies that, along with LSI Logic, created the ASIC business. One challenge in ASIC is that the customer needs to decide which ASIC company to use (since the libraries and technologies are all different) meaning they needed to get quotes from several companies.… Read More

Amorphous Silicon and TFTs

Most ICs are fabricated with crystalline silicon (c-Si), which is a tetrahedral structure forming a well-ordered crystal lattice. There’s another form of semiconductor material called amorphous silicon (a-Si) which has no long-range periodic order. It turns out that a-Si is a great material for the active layer in thin-film… Read More

Adding a Digital Block to an Analog Design

My engineering background includes designing at the transistor-level, so I was drawn to attend a webinar today presented by Tanner EDAand Incentia about Adding a Digital Block to an Analog Design. Many of the 30,000 users of Tanner tools have been doing AMS designs, so adding logic synthesis and static timing analysis from Incentia… Read More

Finding Logic Issues Early that Impact Physical Implementation

Complex SoC project teams typically use a divide and conquer approach where specialized engineers work in separate domains, like front-end or back-end. The five major engineering tasks for IC design can be described as: RTL design, synthesis, floor planning, place and route, then finally design analysis.

What if you could detect… Read More