My first exposure to running something virtual on a computer was when I decided to run the Windows OS on my MacBook Pro using software provided by Parallels. With that virtualization I was able to run the Quicken app under Windows on my MacBook Pro, along with the popular Internet Explorer web browser. The app performance on virtualized… Read More

Tag: webinar

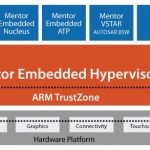

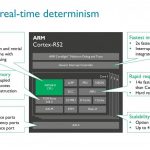

ARM and Mentor talk about Real Time Virtualization, Webinar

Processor cores come in a wide variety of speeds, performance and capabilities, so it may take you some time to find the proper processor for your system. Let’s say that you are designing a product for the industrial, automotive, military or medical markets that has an inherent requirement for safety, security and reliability… Read More

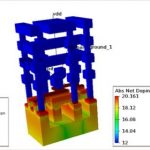

It’s Better than SUPREM for 3D TCAD

Process and device engineers have a tough task to model and simulate an IC process prior to fabricating silicon, however this approach is much better than the alternative choice in the 1970’s of just running multiple lots of wafers and then making measurements to see if your node was meeting specifications. Out of Stanford… Read More

Mentor Webinar Series: Integrating the Systems Engineering Flow

Product lifecycle management is probably not the most gripping topic for most design engineers. You want to get on with architecture, design, verification and implementation. But if you are building products for any safety-sensitive application in a car, a medical appliance, avionics, railway applications in Europe – to name… Read More

Achieving Lower Power through RTL Design Restructuring (webinar)

From a consumer viewpoint I want the longest battery life from my electronic devices: iPad tablet, Galaxy Note 4 smart phone, Garmin Edge 820 bike computer, and Amazon Kindle book reader. In September I blogged about RTL Design Restructuring and how it could help achieve lower power, and this month I’m looking forward to … Read More

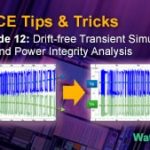

Drift is a Bad Thing for SPICE Circuit Simulators

My first job out of college was with Intel, located in Aloha, Oregon and I did circuit simulations using a proprietary SPICE circuit simulator called ASPEC that was maintained in-house. While doing some circuit simulations one day I noticed that an internal node in one of my circuits was gradually getting higher and higher, even… Read More

Power-Aware Debug to Find Low-Power Simulation Bugs

When I worked at Intel designing custom chips my management would often ask me, “Will first silicon work?” My typical response was, “Yes, but only for the functions that we could afford to simulate before tape-out.” This snarky response would always cause a look of alarm, quickly followed by a second … Read More

Catching low-power simulation bugs earlier and faster

I’ve owned and used many generations of cell phones, starting back in the 1980’s with the Motorola DynaTAC phone and the biggest usability factor has always been the battery life, just how many hours of standby time will this phone provide and how many minutes of actual talk time before the battery needs to be recharged… Read More

Webinar alert – another break in the memory wall

A couple months ago we heard from another vendor in a webinar on HBM and breaking through the “memory wall”. Next week Open Silicon weighs in on the topic in a webinar with partners SK Hynix and Synopsys.… Read More

Process Development, CAD and Circuit Design

Working at Intel as a circuit designer I clearly remember how there were three distinct groups: Process Development, CAD and Circuit Design. Each of the groups sat in a different part of the building in Aloha Oregon, we had different job titles, different degrees, spoke with different acronyms and yet we all had to work together … Read More