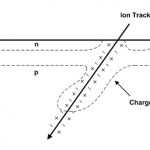

Single Event Effects (SEE) are important because we depend upon our consumer, industrial and aerospace products to work reliably. Protons, electrons, neutrons, or alpha particles may perturb the MOS or bipolar device operation in either a destructive or non-destructive fashion. Galactic cosmic rays are one source of these… Read More

Tag: webinar

Single Event Upsets

Do you know what a SEE is? It stands for single event upset. We live on a radioactive planet which is also bombarded with cosmic rays, so particles are bombarding our chips. The materials used in packaging also can create particles that cause problems, even the solder. Reliability and aging has been an area that has not been at the forefront… Read More

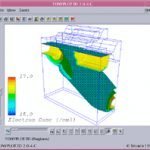

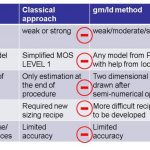

Full-Custom Low Power Design Methodology

Digital designers have used logic optimization and logic synthesis for decades as a means to produce more optimal designs with EDA tools. On the analog and transistor-level side of design the efforts to automatically optimize for speed or power have generally been limited to circuits with only a handful of transistors. These … Read More

Learning an HDL Simulator

Learning an HDL language or an HDL simulator are two different things, so I wanted to see what was available for learning a vendor-specific HDL simulator. I’ve already taught Verilog as an instructor using both ModelSim and Active-HDL simulators, however we only used a handful of commands in the class and labs in order to … Read More

Addressing MCU Mixed Signal Design Challenges

The emerging market for IoT and wearable devices are designed with mixed-signal IP that includes: embedded CPU, flash, analogue and radio.EDA and IP companies have recently worked together to allow us to design an MCU with mixed-signal IP blocks more efficiently. This morning I attended a webinar with presenters from ARMand … Read More

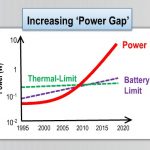

Early RTL Power Analysis and Reduction

Power analysis and reduction for SoC designs is a popular topic because of our consumer electronics dominated economy, and the need to operate devices on a battery source for the maximum time before a recharge. Just from my desk I can see multiple battery-powered devices: Laptop, tablet, smart phone, e-book reader, bluetooth … Read More

Migrating to Andes from 8051

The 8051 microcontroller has been around for years…decades in fact. It was originally developed in 1980 by Intel. Back then it required 12 clock cycles per instruction but modern cores use just one. While it is still widely used, mostly as an IP core for SoCs, it is running out of steam despite running over 50 times faster than… Read More

Known Unknowns and Unknown Unknowns

Donald Rumsfeld categorized what we knew into known unknowns and unknown unknowns. In a chip design, those unknown unknowns can bite you and leave you with a non-functional design, perhaps even intermittent failures which can be among the hardest problems to debug.

Chips are too big to do any sort of full gate-level simulation,… Read More

Low-Power Design Webinar – What I Learned

You can only design and optimize for low-power SoC designs if you can actually simulate the entire Chip, Package and System together. The engineers at ANSYS-Apachehave figured out how to do that and talked about their design for power methodology in a webinar today. I listened to Arvind Shanmugavel present a few dozen slides and… Read More

Analog ECOs and Design Reviews: How to Do Them Better

One of the challenges in doing a complex analog or mixed signal design is that things get out of step. One designer is tweaking the schematic and re-simulating, another is tweaking the layout of transistors, another is changing the routing. This is not because the design flow is messed up, but rather it reflects reality. If you wait… Read More