We’re putting the finishing touches on Chapter 9 of our upcoming book on ARM processors in mobile, this chapter looking at the evolution of Qualcomm. One of the things that made Qualcomm go was their innovative use of digital simulation. First, simulation proved out the Viterbi decoder (which Viterbi wasn’t convinced had a lot … Read More

Tag: modeling

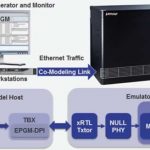

Testing Ethernet with virtual co-modeling

Ethernet is suddenly a hot topic in SoC design again. The biggest news may be this: it’s not just the cloud and enterprise networks. Those are still important applications. The cloud is driving hard for more ports at 25G server and 100G switch speeds according to a recent Dell’Oro Group report. Enterprise networks are driving for… Read More

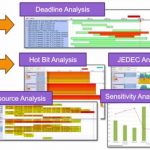

DDR stands for Don’t Do (Just) RTL

In optimizing SoC design for performance, there is so much focus on how fast a CPU core is, or a GPU core, or peripherals, or even the efficiency of the chip-level interconnect. Most designers also understand selecting high performance memory at a cost sweet spot, and optimizing physical layout to clock it as fast as possible within… Read More

A Brief History of ASTC and VLAB Works

When I worked for VaST our engineering was in Sydney Australia. To my surprise there was another, entirely independent, group working on virtual platform modeling and tools in another place in Australia, in Adelaide. Is there something in the Fosters? They had originally been part of Motorola Corporate R&D and Software Group,… Read More

Power Management Policies for Android Devices

I’ll never forget the shock when I upgraded from a Feature Phone to my first Android-powered SmartPhone, because all of a sudden my battery life went from 6 days down to only 1 day between charges. As a consumer, I really want my battery to last much longer than one day, so the race is on for mobile phone companies to design their… Read More

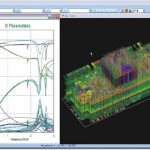

Single Event Upsets

Do you know what a SEE is? It stands for single event upset. We live on a radioactive planet which is also bombarded with cosmic rays, so particles are bombarding our chips. The materials used in packaging also can create particles that cause problems, even the solder. Reliability and aging has been an area that has not been at the forefront… Read More

Book review: “shift left” with virtual prototypes

Shipping a product with complete software support at official release is a lot more difficult than it sounds. Inevitably, there is less than enough hardware to go around, and what little there is has to fill the needs of hardware designers, test and certification engineers, software development teams, systems integration teams,… Read More

How to Develop Accurate Yet High Performance Models

In today’s environment of semiconductor design, SoCs are crammed with various IPs with multiple functionalities and processors integrated together. In such an event it has become necessary to model the system and verify on Virtual Platform before getting into actual design and fabrication. And that requires modelling of each… Read More

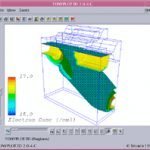

Signal integrity: more than just SerDes analysis

When Cadence acquired Sigrity in 2012, two motives were involved: get more competitive in state of the art signal integrity analysis, and grab a foothold into the other vendor’s PCB flows in an area that is developing as a real sore spot for digital designers.

Just as the days where PCB tape-out meant actually using tape are over, … Read More

When the lines on the roadmap get closer together

Tech aficionados love roadmaps. The confidence a roadmap instills – whether using tangible evidence or just a good story – can be priceless. Decisions on “the next big thing”, sometimes years and a lot of uncertain advancements away, hinge on the ability of a technology marketing team to define and communicate a roadmap.

Any roadmap… Read More