Performance, Power and Area (PPA) metrics are the driving force in the semiconductor market and impact all electronic products that are developed. PPA tradeoff decisions are not engineering decisions, but rather business decisions made by product companies as they decide to enter target end markets. As such, the sooner a company… Read More

Tag: cts

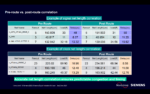

APR Tool Gets a Speed Boost and Uses Less RAM

Automatic Place and Route (APR) tools have been around since the 1980s for IC design teams to use, and before that routing was done manually by very patient layout designers. Initially the big IDMs had their own internal CAD groups coding APR tools in house, but eventually the commercial EDA market picked up this automation area,… Read More

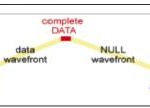

Maybe Clockless Chip Design’s Time has Come

There have always been novel technologies vying to compete with conventional design practices. It is hit or miss on the success of these ideas. In the 90’s I recall speaking to someone who was convinced that they could effectively build computers based on multilevel logic. This, as we know did not pan out. But there have been many … Read More

How Good Are Your Clocks?

One of the trickiest tasks in designing a modern SoC is getting the clock tree(s) right. The two big reasons for this:

- the clocks can consume 30% or more of the power of the whole chip, so minimizing the number of buffers inserted is critical to keeping power under control

- the clock insertion delay and clock skew have a major impact on

Cadence’s New Implementation System Promises Better TAT and PPA

On Tuesday Cadence made a big announcement about their new physical implementation offering, Innovus, during the keynote address at the CDNLive event in Silicon Valley. Cadence CEO Lip-Bu Tan alluded to it during his kick off talk, and next up Anirudh Devgan, Senior Vice President, Digital & Signoff Group, filled in more … Read More

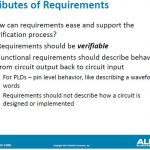

Living with DO-254? You need Aldec!

I will say that as popular as DO-254 and the like is, I am not the fella for that. It can take the simplest of designs into a realm of test and verification like you have never seen before. Yes, when I am flying I happen to be a big fan of this rigorous testing but you will not find me doing that job anytime soon. While the topic is very dry, it … Read More

A Tool Conceived With Designers’ Input and Developed from Scratch

If we look at the past, most of the EDA tools in the semiconductor design space have originated from a designers’ need to do things faster. Regardless of whether it is design exploration, manual design, simulation, verification, optimization (Power Performance Area – PPA) and many other steps in the overall design flow.… Read More

20nm IC production needs more than a ready Foundry

I think by now all of us know, or have heard about 20nm process node, its PPA (Power, Performance, Area) advantages and challenges (complexity of high design size and density, heterogeneity, variability, stress, lithography complexities, LDEs and so on). I’m not going to get into the details of these challenges, but will ponder… Read More

Properly Handing Of Clock Tree Synthesis Specifications

Given today’s design requirements with respect to low power, there is increasing focus on the contribution to total power made by a design’s clock trees. The design decisions made by the front-end team to achieve high performance without wasting power must be conveyed to back-end team. This hand-off must be accurate… Read More

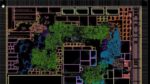

Schematic, IC Layout, Clock and Timing Closure from ICScape

Before this DAC I had never even heard of ICScape, so on Monday and Wednesday I visited their booth to find out their story.

Steve Yang, Ph.D. (Co-founder and President), Ravi Ravikumar (Marketing)

ICScape was founded in 2005 in Santa Clara by Steve Yang (Circuit Design engineer for microprocessor, Synopsys) and Jason Xing (Sun… Read More