As SoC and IP designs continue to increase in complexity while schedules accelerate, verification teams are looking for methodologies to improve design confidence more quickly. Formal verification techniques provide one route to improved design confidence, and the increase in papers and interest at industry conferences… Read More

Tag: amd

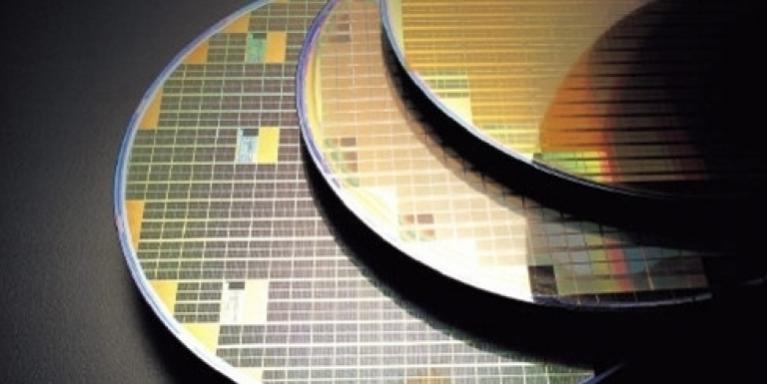

The real race for superiority is TSMC vs Intel

Recent talk of AMD vs Intel market share share is misguided, the real race for superiority is TSMC vs Intel underlying that, tech dominance between US & China.

There has been much discussion of late about market share between Intel and AMD and how much market share AMD will gain at Intel’s expense due to Intel’s very… Read More

Data Security – Why It Might Matter to Design and EDA

According to the Economist, “The world’s most valuable resource is no longer oil, but data”. Is this the case?Data is the by-product ofmany aspects of recent technology dynamics and is becoming the currency of today’s digital economy. All categories in Gartner’s Top10 Strategic Technology Trends for 2018 (Figure… Read More

Choosing the lesser of 2 evils EUV vs Multi Patterning!

For Halloween this week we thought it would be appropriate to talk about things that strike fear into the hearts of semiconductor makers and process engineers toiling away in fabs. Do I want to do multi-patterning with the huge increase in complexity, number of steps, masks and tools or do I want to do EUV with unproven tools, unproven… Read More

Synopsys Opens up on Emulation

Synopsys hosted a lunch panel on Tuesday of DAC this year, in which verification leaders from Intel, Qualcomm, Wave Computing, NXP and AMD talked about how they are using Synopsys verification technologies. Panelists covered multiple domains but the big takeaway for me was their full-throated endorsement of the ZeBu emulation… Read More

AMD vs Intel Update!

Is it just me or has AMD just pulled off one of the most amazing semiconductor comebacks of the century? Let’s take a closer look.

Who doesn’t long for the days when Intel and AMD went head to head in the battle for microprocessor supremacy? Back then Intel, was still operating under the Andrew Grove mantra of “Only the Paranoid Survive”… Read More

Soitec – Enabling the FDSOI Revolution

Recently I published two blogs on Fully Depleted Silicon On Insulator (FDSOI) and the potential the technology shows for a variety of low power and wireless applications. In order to produce FDSOI devices, the device layer has to be thin enough to ensure the device is fully depleted and ideally the buried oxide has to be thin enough… Read More

AMD Zen and the Art of Microprocessor Maintenance

AMD is a fantastic company with highly talented people, but for some reason just hasn’t managed to put a winning streak of microprocessor architectures back-to-back. It’s frustrating to watch: they ride like mad to catch up to or even pull slightly ahead of Intel, then fall back in the pack when they have to make an extended pit stop,… Read More

Why is AMD Stock Jumping?

One of my favorite pastimes is listening to the quarterly investor calls of the leading semiconductor companies. I can then match up the talking points with the calls I do with Wall Street, the conferences I attend, and the other data points I have collected while working inside the fabless semiconductor ecosystem for more than … Read More

AMD’s 7th Generation APU Brings Many Performance Tweaks And The Last Hurrah Before Zen

Advanced Micro Devices has already told us that 2016 was going to be the year of graphics, but the reality is that they also have a lot going on in their CPU and APU division as well. In fact, in addition to Advanced Micro Devices’s newly announced 7th Generation APUs in 2016, the company is also expected to launch their new Zen CPU cores… Read More