You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

ARM 64-bitby Paul McLellan on 10-30-2012 at 6:56 pmCategories: Arm, IP

AMD announced yesterday that they would be building 64-bit ARM-based chips intended for use in servers. What was unclear is what the processors would be like. Although ARM had announced that they would move into 64-bit processors they didn’t have any that they had actually announced as being available for licensing.

At … Read More

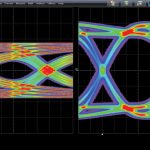

FPGA Prototyping is growing in popularity as a method to get an SoC design into hardware running at clock speeds up to 100MHz or so. One downside during traditional FPGA prototyping debug is the limited number of internal signals that you can observe while trying to chase down bugs in the hardware design in the presence of running … Read More

I’ve talked before about how Apple and Samsung make most of the money in the handset business (and also about how Nokia…er…doesn’t). Now there is a report from Canaccord Genuity makes it clear just how much of the profit they make: 106%. And that is down from second quarter when they made 108%.

How can they… Read More

Jasper restructured JasperGold so that it could deliver its formal technology more flexibly by having a base system and a porfolio of apps. This would also make it easier to upgrade capabilities by creating new apps. Today, Jasper announced two new apps:

- JasperGold Structural Property Synthesis (SPS)

- JasperGold Behavioral

…

Read More

A funny thing happened at dinner the other night. The SemiWiki blog “8 Things I Hate about My iPhone5” caused quite a discussion. Half the table had Samsung phones and the other half iPhones. It really was more of a religious or political debate versus a rational consumer electronic discussion. An interesting side note, it seems … Read More

At DAC in June I visited and blogged about 30+ EDA and Semi IP companies, however I didn’t have time to watch the TowerJazz presentation in the Cadence Theater entitled: AMS Flow for Power Management Designs. Today I watched the 26 minute video and have summarized what I learned in this blog post.… Read More

“Simulation: Expert Insights into Modeling Microcontrollers” was the recent panel hot topic at Renesas DevCon2012, featuring Paolo Giustoof GM, Mark Ramseyerof Renesas, Marc Serughettiof Synopsys, Jay Yantchevof ASTC / VWorks, and Simon Davidmannof Imperas.

… Read More

They say what adds value is to take something difficult and make it look simple. USB looks so simple when it is done right, but designers know it can be one of the more tempermental features in an SoC, especially in the latest SuperSpeed incarnation.… Read More

There’s been an interesting trend emerging the past couple of years; a gentrification, if you will, of the ASIC business. What was thought to be a dying supply chain model has re-emerged as a health and growing segment of the semiconductor industry. Recent figures from Gartner place 2012 ASIC revenue at around $24.4 billion… Read More

Brian Bailey at EETimes has an interesting interview with Kathryn Kranen. He says that the interview will be published in installments but the first one is up here. This first installment is mostly about how long-lived EDA companies (and others) have become since it takes a long time to build up enough revenue to be able to IPO.

She… Read More

Solving the EDA tool fragmentation crisis