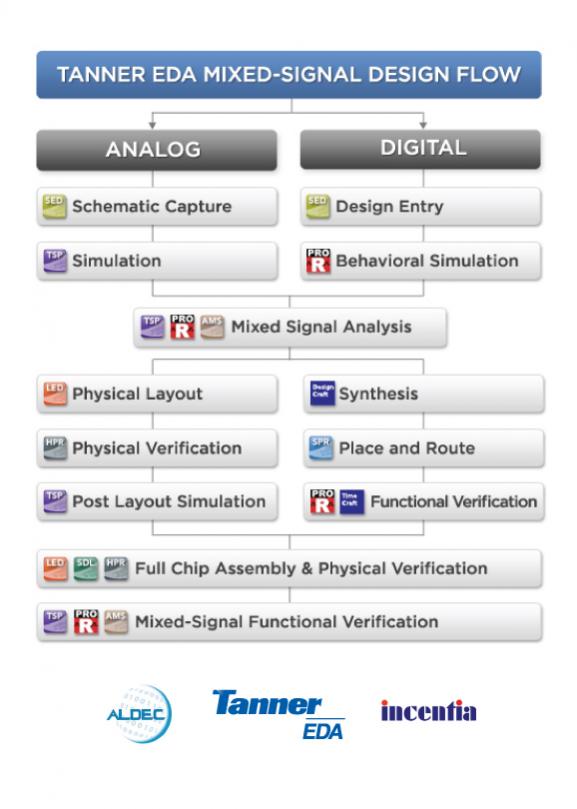

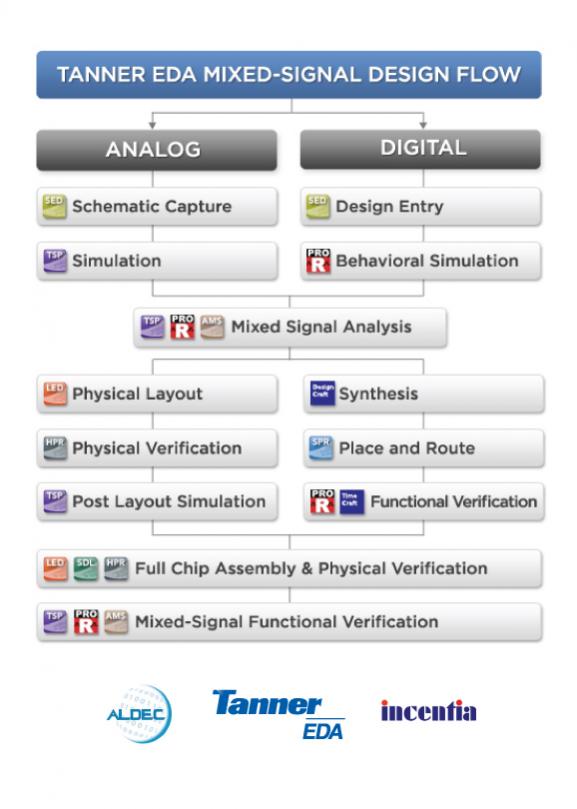

EDA tools come in all sizes and price ranges, so I was pleased to readthat Tanner EDAhas completed an integration with Incentia. A few months ago Tanner announced their integration with Aldec for digital simulation, and today’s announcement extends their tool suite to include digital synthesis and static timing. Here’s the entire integrated AMS tool flow:

The two specific EDA tools integrated from Incentia in the flow are:

- Logic Synthesis – DesignCraft

- Static Timing Analysis – TimeCraft

Where would you use such a tool flow? Mostly in AMS designs where you have big Analog and little Digital.

The benefit to an integrated design flow is that you go to just one vendor for support, Tanner EDA. You stay inside of the Tanner tools to launch the logic synthesis and static timing tools. The versions of software from both companies have been tested and proven to work, so you don’t have to rely upon a CAD team to keep your design flow working.

Some of the features of TimeCraft for Static Timing Analysis:

- Easy to adopt: compatible usage, SDC, .lib/CCS/ECSM, Tcl based scripting

- Supports both SDF annotation and SPEF delay calculation flows

- Proven signoff accuracy and correlation

- Rich features, including image save & restore, Static IR-drop aware STA, Voltage /

- temperature scaling, CPF & UPF support, pulsed latch timing analysis, etc.

- Advanced stage & distance based OCV with rich features for less pessimistic analysis

- Advanced multi-thread technology: further 2X to 5X speedup

- Fast runtime: 2X to 8X faster than other solutions for big designs

- Slim memory usage enabling analysis for extremely large designs

- Highly efficient multi-task MMMC allowing for analyzing more corners in much less time

- Numerous customer tape-outs, including using 40nm process and designs over 50M gates

DesignCraft features for logic synthesis include:

- Patented based technologies for sequential, low power, and DFT synthesis

- Easy to adopt: compatible usage, Verilog/VHDL, SDC, NLDM .lib / CCS

- Highly crafted architectures and implementations for data-path & logic operator components (e.g. adder, multiplier, and many others) for best constraint optimizations

- Low power synthesis: clock gating, operator isolation, leakage power optimization, power analysis

- DFT synthesis: scan cell replacement, DFT rule violation checking and fixing, scan chaining and stitching, DFT preview & reporting

- Largest amount of area and power reduction while meeting timing constraints

- Fast runtime: 5M gates within 2 hours

- Proven through many customer tape-outs

Comments

There are no comments yet.

You must register or log in to view/post comments.