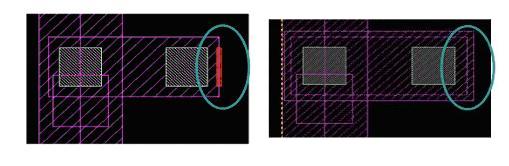

A High-Definition Multimedia Interface (HDMI) IP core was being implemented in an advanced process technology. This fairly large and complex analog mixed-signal (AMS) IP comprising over 130K devices was close to being finalized and shipped to the customer. But many design rules at the foundry were unexpectedly changed from… Read More

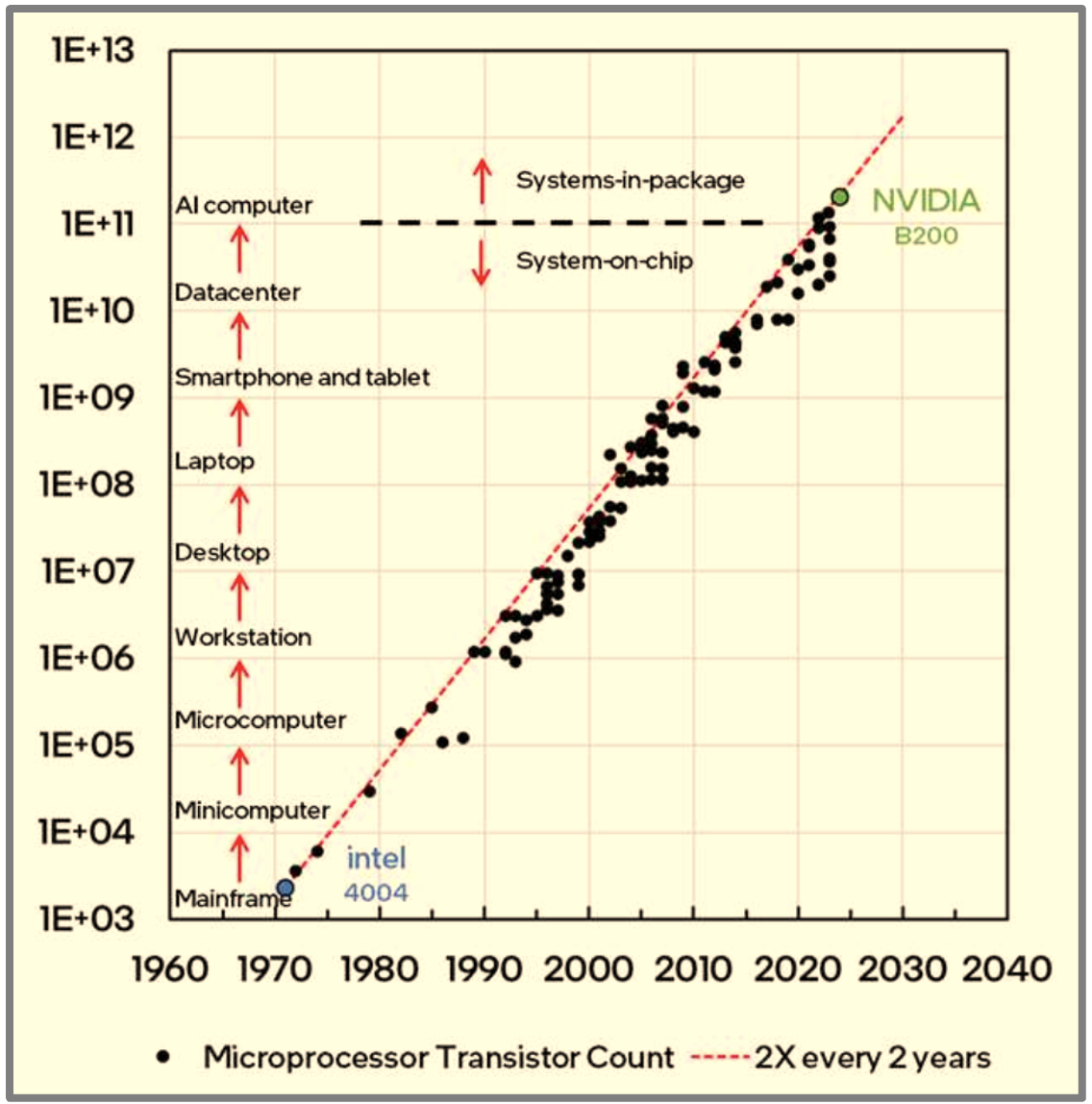

An Invited Talk at IEDM: Intel’s Mr. Transistor Presents The Incredible Shrinking Transistor – Shattering Perceived Barriers and Forging AheadIEDM turned 70 last week. This was cause…Read More

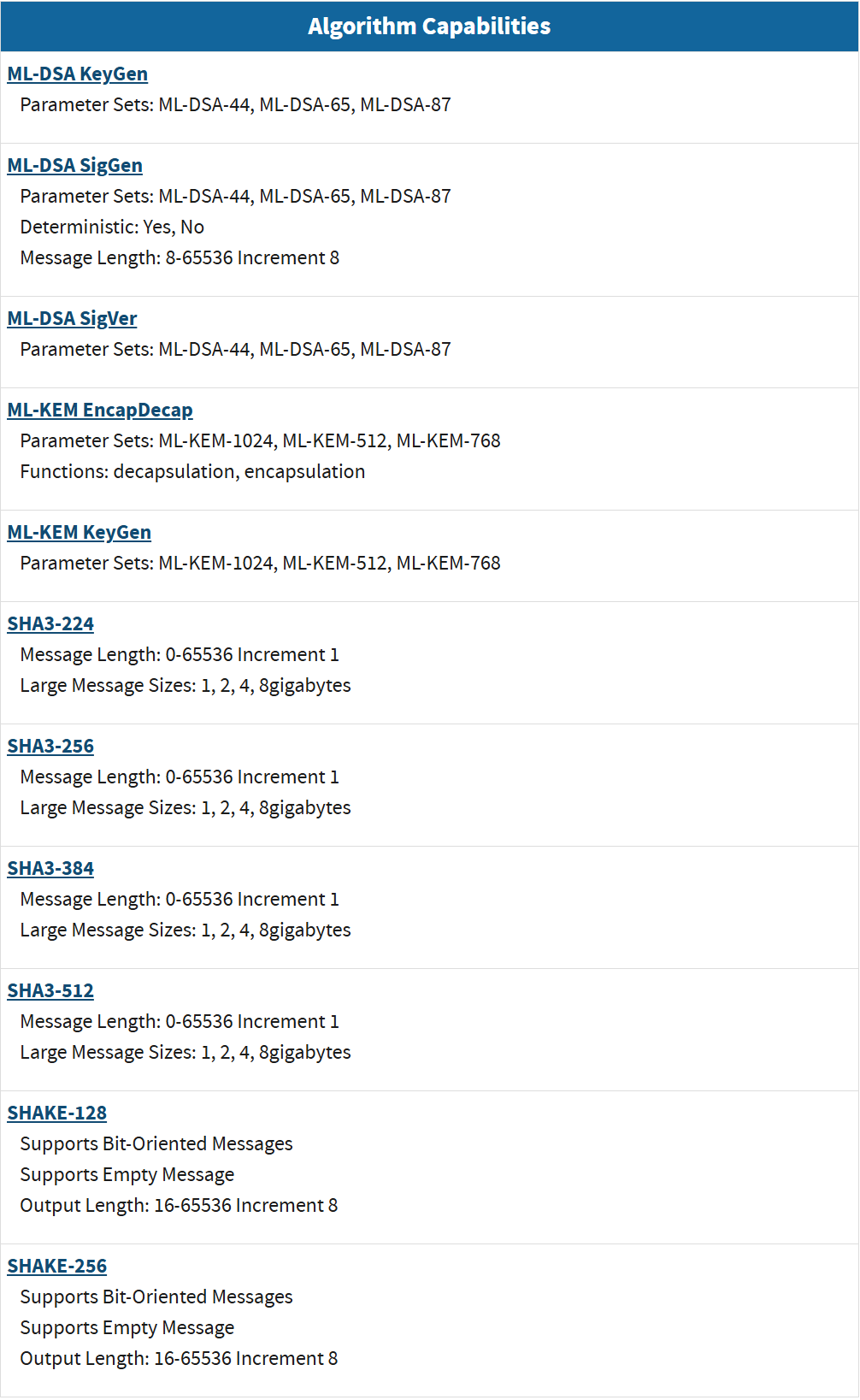

An Invited Talk at IEDM: Intel’s Mr. Transistor Presents The Incredible Shrinking Transistor – Shattering Perceived Barriers and Forging AheadIEDM turned 70 last week. This was cause…Read More Certification for Post-Quantum Cryptography gaining momentumA crucial step in helping any new technology…Read More

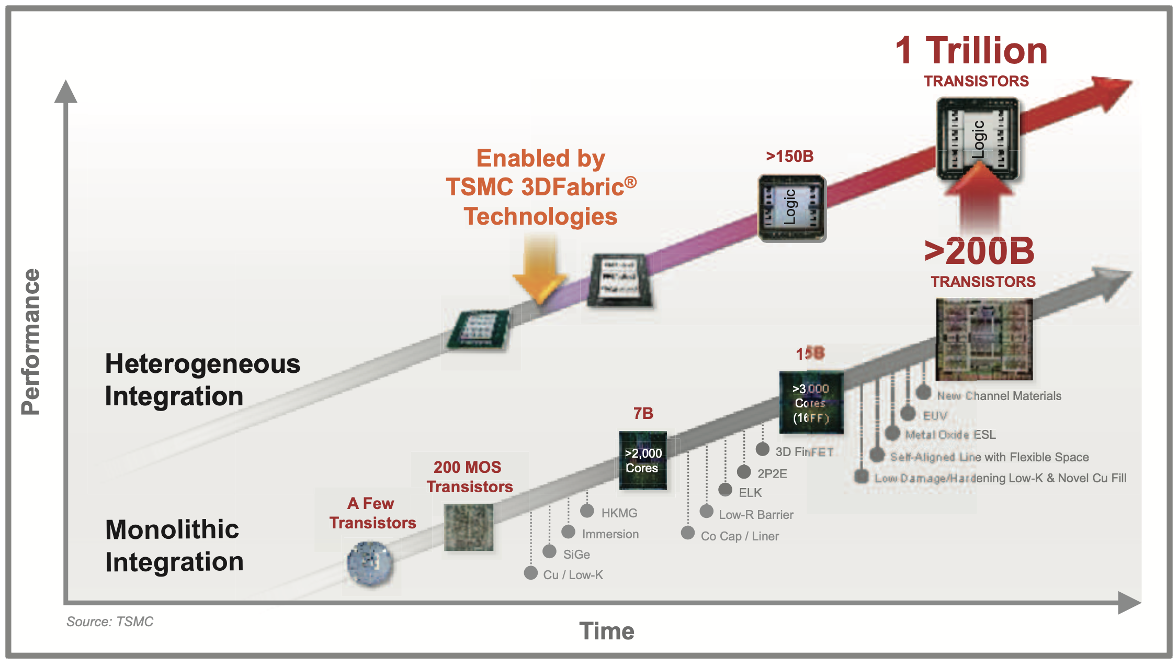

Certification for Post-Quantum Cryptography gaining momentumA crucial step in helping any new technology…Read More IEDM Opens with a Big Picture Keynote from TSMC’s Yuh-Jier MiiThe main program for the 70th IEDM opened…Read More

IEDM Opens with a Big Picture Keynote from TSMC’s Yuh-Jier MiiThe main program for the 70th IEDM opened…Read More How I learned Formal VerificationBing Xue is a dedicated Formal Verification Engineer at Axiomise,…Read More

How I learned Formal VerificationBing Xue is a dedicated Formal Verification Engineer at Axiomise,…Read MoreShakeup at Mentor Graphics

Reading the title you guessed it right, Mentor Graphics has three new board members today from the slate offered by billionaire activist Carl Icahn:

- José Maria Alapont, chief executive of the auto parts maker Federal-Mogul

- Gary Meyers, a director of the chip maker Exar

- David Schechter, an executive at Mr. Icahn’s investment firm

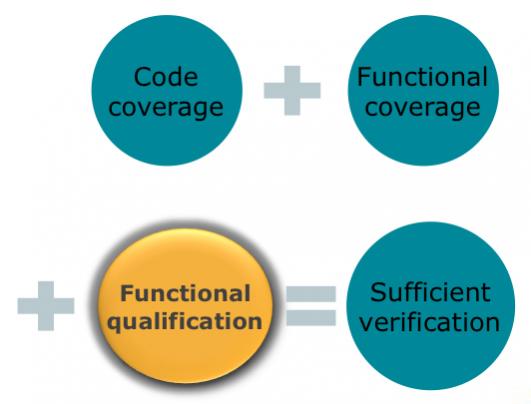

How Good is Your Verification?

The traditional way for analyzing the effectiveness of testing in the software world and in the RTL world is code coverage. Make sure that every line of code is executed. This is a pretty crude measure since even 100% code coverage doesn’t mean that all the condition has really been tested but it is certainly necessary–after… Read More

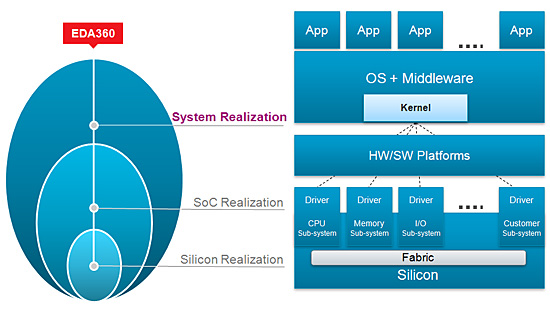

SOC Realization: How Chips Are Really Designed

If you just casually peruse most marketing presentations by EDA companies, you’d come to the conclusion most SoCs are designed from scratch, wrestlilng the monster to the ground with bare hands. But the reality is that most SoCs consist of perhaps 90% IP blocks (many of them memories). That still leaves the remaining 10% … Read More

Cadence EDA360 is Paper!

Hard to believe a year has gone by since the big announcement of the Cadence Blueprint toBattle ‘Profitability Gap’; Counters Semiconductor Industry’s Greatest Threat! Having spent more time on it that I should have, here is my opinion on EDA360 on its first anniversary.

Richard Georing did a very nice anniversary piece “Ten Key… Read More

40nm to 28nm Migration Success Story

The problem:To move dual-port SRAM library and macros from a 40nm process to a 28nm process. In addition to all the changes between two different foundry processes, the 28nm rules are disruptive and incompatible with the previous rules. The memory corecells (foundry-specific) would also need to be completely replaced.

Current… Read More

Intel’s 22nm Process. Atom, ARM, Apple

Intel had a big press event yesterday at which they announced details of their 22nm process. In a change from their current processes, it goes with a vertical gate. In fact 3 gates which gives them much better control of leakage through transistors that are switched off, along with more transmission through the on transistors. They… Read More

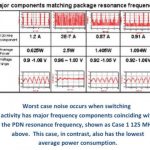

Chip Power Models

As the complexity of the chip-package-system (CPS) interactions has increased, the tradeoffs in doing a power and noise analysis has had to gradually increase. As is so often the case in semiconductor designs, issues first arise as second-order effects that can largely be ignored but each process node makes the problem worse … Read More

Apache at DAC

DAC is less than a month away, June 6-8th for the tradeshow, longer depending on what other events you might also be attending. Apache is in booth 2448 (marked in red on the DAC floorplan map.

Many of the presentations at the Apache booth will be customers (such as ARM, Xilinx, ST Ericsson, GlobalFoundries and TSMC) discussing various… Read More

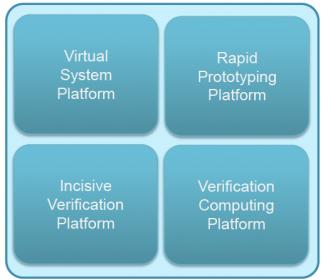

Two New Platforms for Systems Designers

Introduction

Today Cadence announced at the Embedded Systems Conference something of interest to systems designers.

What’s New?

The Rapid Prototyping Platform and Virtual System Platform are what’s new, and they intend to enable and automate concurrent hardware and software development. I can remember Mentor… Read More

The Intel Common Platform Foundry Alliance