The announcement that Paul Otellini will step down in May 2013 is extraordinary in the history of the way Intel makes CEO transitions. They are thoughtful, deliberate and years in the making, unlike today’s announcement. Twenty years ago Otellini and Andy Bryant were in the top echelon of Andy Grove’s executive team and … Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreIs The Fabless Semiconductor Ecosystem at Risk?

Ever since the failed Intel PR stunt where Mark Bohr suggested that the fabless semiconductor ecosystem was collapsing I have been researching and writing about it. The results will be a book co-authored by Paul McLellan. You may have noticed the “Brief History of” blogs on SemiWiki which basically outline the book. If not, start… Read More

Here to make my stand, with a chipset in my hand

Yesterday, I clicked “like” on a LinkedIn post with the title “TI Cuts 1,700 Jobs”. Today, I read the analysis and pulled out Social Distortion’s “Still Alive” for inspiration. I’ve been through this more than once. For them it’s not like-worthy, and I feel their sting.

The part of the post I liked was the comment: “This is good for … Read More

Mentor and NXP Demonstrate that IJTAG Can Reduce Test Setup Time for Complex SoCs

The creation of test patterns for mixed signal IP has been, to a large extent, a manual effort. To improve the process used to test, access, and control embedded IP, a new IEEE P1687 standard is being defined by a broad coalition of IP vendors, IP users, major ATE companies, and all three major EDA vendors. This new standard, also called… Read More

What I Learned About FPGA-based Prototyping

Today I attended an Aldec webinar about ASIC and SoC prototyping using the new HES-7 Board. This prototyping board is based on the latest Virtex-7 FPGA chips from Xilinx.

You can view the recorded webinar here, which takes about 30 minutes (should be available in a few days). I first blogged about the HES-7 two months ago, ASIC Prototyping… Read More

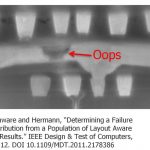

Test and Diagnosis at ISTFA

Finding and debugging failures on integrated circuits has become increasingly difficult. Two sessions at ISTFA (International Symposium for Testing and Failure Analysis) on Thursday address the current best practices and research directions of diagnosis.

The first was a tutorial this morning by Mentor Graphics luminary… Read More

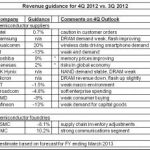

Semiconductor market negative in 2012

September WSTS data shows the 3Q 2012 semiconductor market increased 1.8% from 2Q 2012. The year 2012 semiconductor market will certainly show a decline. 4Q 2012 would need to grow 11% to result in positive growth for 2012. The outlook for key semiconductor companies points to a 4Q 2012 roughly flat with 3Q 2012. The table below shows… Read More

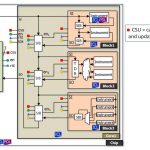

Creating Plug-and-Play IP Networks in Large SoCs with IEEE P1687 (IJTAG)

Until now, the integration and testing of IP blocks used in large SOCs has been a manual, time consuming design effort. A new standard called IEEE P1687 (or “IJTAG”) for IP plug-and-play integration is emerging to simplify these tasks. EDA tools are also emerging to support the new standard. Last week mentor announcedTessent IJTAG,… Read More

Adesto Acquisition of Atmel Serial Flash: Strange Bedfellows?

On October 1, Adesto Technologies announced that it had acquired Atmel’s DataFlash and Serial Flash business groups. At first sight, this seemed a rather counter intuitive move for one of the most aggressive (and visible) companies in the emerging memory field. The purchase raised many questions to those, not least the moderator… Read More

The logic of trusting FPGAs through DO-254

Any doubters of the importance of FPGA technology to the defense/aerospace industry should consider this: each Airbus A380 has over 1000 Microsemi FPGAs on board. That is a staggering figure, especially considering the FAA doesn’t trust FPGAs, or the code that goes into them.… Read More

Solving the EDA tool fragmentation crisis