At Semicon, Ben Rathsack of Tokyo Electron America talked about directed self assembly (DSA) at the standing-room only lithography morning. So what is it? Self assembly involves taking two monomers that don’t mix and letting them polymerise (so like styrene forming polystyrene). Since they won’t mix they will … Read More

MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More

MZ Technologies Launches Advanced Packaging Design Video SeriesIn a significant move aimed at empowering semiconductor…Read More Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More

Superhuman AI for Design Verification, Delivered at ScaleThere is a new breed of EDA emerging.…Read More The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read More

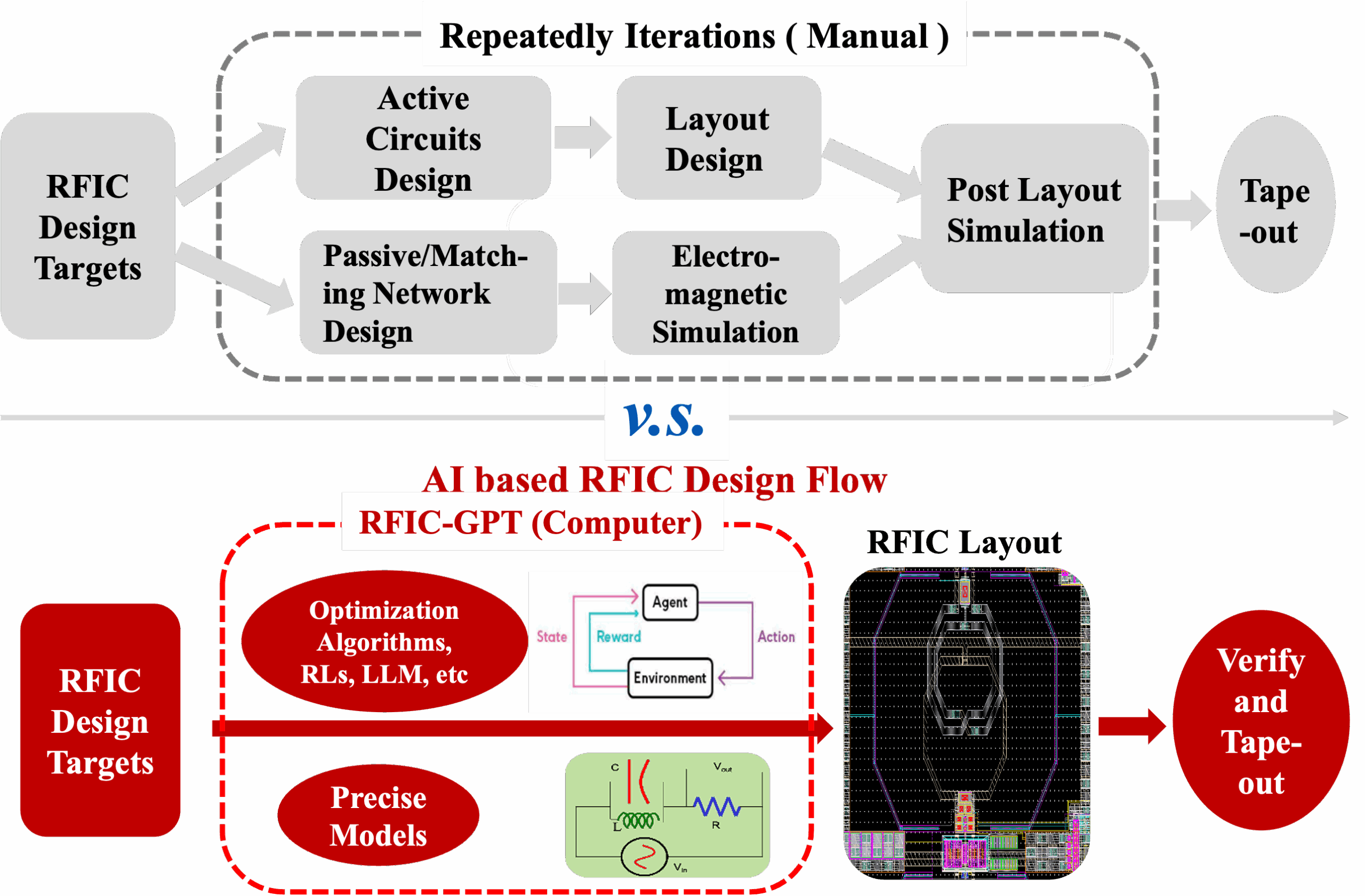

The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the DefenseIndustrial control systems (ICS) underpin the world’s most…Read More Radio Frequency Integrated Circuits (RFICs) Generated by AI Based Design AutomationBy Jason Liu, RFIC-GPT Inc. Radio frequency integrated…Read More

Radio Frequency Integrated Circuits (RFICs) Generated by AI Based Design AutomationBy Jason Liu, RFIC-GPT Inc. Radio frequency integrated…Read MoreElectronics markets showing signs of recovery

Electronics markets bounced back strongly in 2010 from the 2008-2009 recession. The recovery stalled in 2011 as a series of natural and human-made disasters hit various parts of the world. Japan was hit by an earthquake and tsunami in March 2011. Thailand was affected by floods which disrupted HDD production and thus impacted … Read More

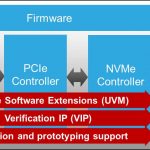

Shorter, better and easier PCIe and NVM Express Verification flow with advanced technologies

We have talked about Cadence subsystem IP strategy, illustrated by NVM Express subsystem IP, in a previous blog. What we said was that “A subsystem IP based approach will also speed up the software development and validation phase: if the IP provider is able to propose the right tools, like the associated Verification IP (VIP), … Read More

Morris Chang Comments on Q2 2012: 28nm, 20nm, 16nm, FinFets, CAPEX, etc…

Twenty eight nanometer is progressing very well. Our output and our yields are both above the plans that we set for ourselves and the plans that we communicated to our customers early in the year. Early in the year means January-February of the year, we set our plans in output and in yields and we, of course, ever since then we tried to… Read More

CEVA-XC4000 new DSP IP core

The CEVA-XC4000 offers unparalleled, scalable performance capabilities and innovative power management to address the most demanding communication standards, including LTE-Advanced, 802.11ac and DVB-T2, on a single architecture. Building upon its highly successful predecessors, the CEVA-XC4000 architecture sets… Read More

TSMC Reports Second Highest Quarterly Profit!

We all knew this quarter would be big but maybe not this big. Not all good news though so keep on reading. The news coverage is all over the map, mostly because they have no idea what a pure-play foundry really is. They also underestimate the power of mobile computing which should be a “Revenue by Application” market segment itself. … Read More

Higgs bosons, (un)certainty, and black holes

Ever since the announcement in early July from CERN that they likely have, probably, finally found the Higgs boson, I’ve been thinking about what quantum mechanics means to our daily ‘classical model’ existence. On the surface, nothing. The most fantastical aspects of quantum mechanics, like uncertainty, tunneling and the … Read More

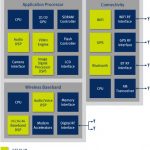

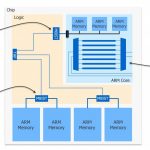

It Takes a Village: Mentor and ARM Team Up on Test

Benjamin Franklin, “I didn’t fail the test, I just found 100 ways to do it wrong.” I was reminded of this line during a joint Mentor-ARM seminar yesterday about testing ARM cores and memories. The complexity of testing modern SoC designs at advanced nodes, with multiple integrated ARM cores and other IP, opens up plenty of room for… Read More

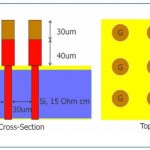

How Do You Extract 3D IC Structures?

The press has been buzzing about 3D everything for the past few years, so when it comes to IC design it’s a fair question to ask how would you actually extract 3D IC structures for use by analysis tools like a circuit simulator. I read a white paper by Christen Decoin and Vassilis Kourkoulos of Mentor Graphics this week and became… Read More

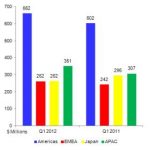

EDAC Announces EDA up 6.3% in Q1 versus 2011

EDAC announced that EDA industry revenue increased 6.3% for Q1 2012 to $1536.9M compared to a year ago. Sequentially it declined, as it normally does from Q4 to Q1, by 9.6%. Every category except services increased revenue and every region increased revenue except for Japan. The full report is available by subscription, of course.… Read More

Quantum Computing Technologies and Challenges