Calypto announced that Sanjiv Kaul is the new CEO. I first met Sanjiv many years ago when he was still at Synopsys when I interviewed for a position there around the time I transitioned out of Compass and went back to the parent company VLSI. I forget what the position was. Then about three or four years ago when I did some work for Oasys… Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

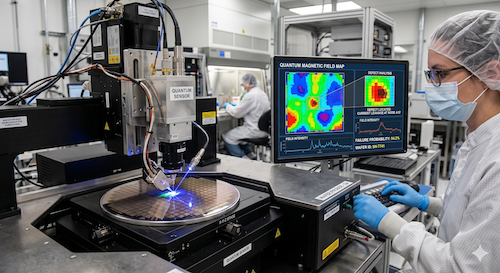

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read MoreSoftware Driven Power Analysis

Power is a fundamentally hard problem. When you have finished the design, you have accurate power numbers but can’t do anything about them. At the RTL level you have some power information but it is often too late to make major architectural changes (add an offload audio-processor, for example). Early in the design, making… Read More

Help, my IP has fallen and can’t get up

We’ve been talking about the different technologies for FPGA-based SoC prototyping a lot here in SemiWiki. On the surface, the recent stories all start off pretty much the same: big box, Xilinx Virtex-7, wanna go fast and see more of what’s going on in the design. This is not another one of those stories. I recently sat down with Mick… Read More

A Brief History of ClioSoft

In the 1990s, software developers were established users of software configuration management (SCM) tools such as open source RCS/CVS or of commercial systems such as Clearcase. Hardware designers, however, managed design data in ad hoc home-grown ways. ClioSoft’s founder, Srinath Anantharaman, recognized that hardware… Read More

SemiWiki Hits Major Readership Milestone!

For those of you who follow SemiWiki and the fabless semiconductor ecosystem it has been a very interesting two years:

The Semiconductor Wiki Project, the premier semiconductor collaboration site, is a growing online community of professionals involved with the semiconductor design and manufacturing ecosystem. Since going… Read More

Common Platform Technology Forum February 5th 2013 Live or Online!

Can’t make it to Santa Clara? Join us online!

The detailed 2013 CPTF agenda is now up in preparation for the February 5th event at the Santa Clara Convention Center. This is one of the rare times that you can get a free lunch! Watch this quick video to see what is in store for us this year. Dr. Paul McLellan and I will be there so please… Read More

Design IP including Multi-standard SerDes enables risk-free, faster customer ASIC designs

ASIC design service companies are an essential piece of the SC ecosystem, as well as Silicon Foundries, EDA and IP vendors. Their customers range from pure fabless with no ASIC design resources, who need a third party to turn a concept into a real product (IC) and then market and sale it, to large IDM temporarily lacking design resource… Read More

Startups: the Biggest Challenge

What is the biggest challenge facing an EDA startup today? By a startup, I mean a brand new company, not a company that already has a few customers and is either on a fast path to success or a slower path whereby the company can continue to grow slowly forever.

Obviously, one challenge is the funding environment. Since EDA acquisitions… Read More

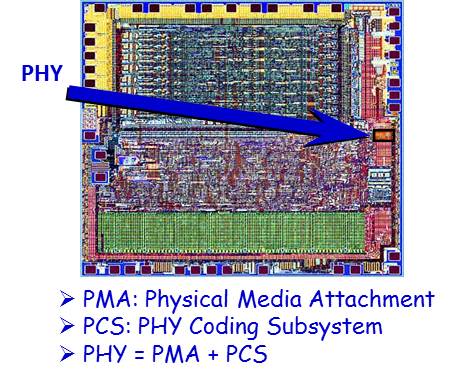

Seeing inside SoC designs, from the beginning

Engineers have this fascination with how things work. They are thrilled to tear stuff apart, and sometimes to even be able to put it back together afterwords. So I can keep my recovering engineer card, I thought I’d take a few moments and look inside a technology Daniel Payne and I have been covering here, exploring where the idea started… Read More

Dynamic/Leakage Power Reduction in Memories

Embedded memories have an important impact on power. SoCs that integrate multiple functions on a single silicon die are at the heart of many electronic devices. As process geometries have scaled, design teams have used more and more of the additional silicon real estate available to integrate embedded memories that serve as scratch-pads,… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior