You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I was the VP marketing at VaST Systems Technology and then at Virtutech. Both companies sold virtual platform technology which consisted of two parts:

- an extremely fast processor emulation technology that actually worked by doing a binary translation of the target binary code (e.g. an ARM) into the native instruction set of the

…

Read More

ARC is a family of configurable processors. Originally it was a standalone company in the UK (what is it with the UK and processor cores?) spun out from Argonaut Software. The A in ARC stood for Argonaut originally. ARC International was acquired by Virage and then Virage was acquired by Synopsys so now it is part of Synopsys Designware… Read More

GlobalFoundries had several interesting things at the ARM TechCon last week. Firstly, GlobalFoundries won the best in show award in the chip design category recognizing the best-in-class technologies introduced since the last TechCon.

Earlier in the summer GlobalFoundries and ARM announced the ARM Cortex-A12 processor,… Read More

Today GSA announced the award nominees for the 2013 awards. They will be presented at the GSA Award Dinner on Thursday December 12th at the Santa Clara Convention Center. The keynote will be given by Steve Forbes.

Recently it was announced that the 2013 Dr. Morris Chang Exemplary Leadership Award winners are CEO and Chairman, Dr.… Read More

Major power reductions are possible by reducing power at the RTL and system levels, and not just at the gate and physical level. In fact, as is so often the case in design, changes can have much more impact when done at the higher level, even given that at that point in the design there is less accurate feedback about changes. Later the… Read More

As I have mentioned before, Paul McLellan and I are writing a book on the history of the fabless semiconductor industry. There is a preview available HERE, it will initially be sold as an e-book on SemiWiki and put into print early next year. Working with Paul McLellan and Beth Martin on this was an amazing experience. The research,… Read More

SoC’s are now dominated by IP blocks sourced either from 3rd parties or internal design teams. This means that IP is now critical to the success of the SoC, yet it is part of the design that teams have the least control over, or visibility into. Most design teams utilize at best ad-hoc methods to manage this IP, and the few that utilize… Read More

Semico’s IMPACT 2013 IP event is next Wednesday November 6th at the DoubleTree Hilton in San Jose.

Here’s what you get if you attend. Keynotes from:

- Kurt Shuler of Arteris. Give him some hard questions about Qualcomm who have just acquired their technology and engineering team

- Chris Rowen of Tensilica, recently acquired

…

Read More

One of the most demanding applications where semiconductors are used is in the various applications of digital video from tablet computers, to home entertainment. iPad with a retina display is already at high-definition (HD) resolution (2048×1536) and all indications are that video is racing towards what is known as 4K… Read More

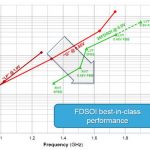

If you have read the excellent article from Paul McLellan, you know about FDSOI as a technology, so I will not come back to FDSOI device, and the comparison with FinFET in term of device topology, doping level and so on. If you missed it, I would recommend you to read this article, as well as the many comments (all of them being relevant).… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior