You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

We all know benchmarks, but do we really understand benchmark results? Benchmark users should always look beyond the simple score when making in-depth technical analysis and request to see all the facts. There are many graphics benchmarks to choose from but let’s name today these three below:

3DMark Ice Stormfrom Futuremark… Read More

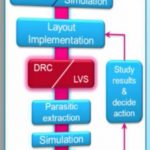

I first visited STat their Agrate, Italy site where Flash memory development is done. At DACthis year Antonio Bogani talked about how ST designs with LDE while using EDA tools and a PDK (Process Design Kit) from Cadence. They recorded the 17 minute presentation, and you can view it herewithout having to register. Antonio’s… Read More

Intel announced their quarterly results today. They beat consensus by a cent. Not surprisingly their business is driven heavily by the microprocessor businesses, what Intel calls PC and Datacenter. Revenue and earnings both set new records in both groups.

As Brian Krzanich, the CEO, said:In the Data Center, we saw double-digit… Read More

The next monthly EDAC mixer is next week on Thursday 23rd October from 6-8pm. It will be at the Sonoma Chicken Coop at 90 Skyport Drive in San Jose (right next to where Magma used to be and Atmel is). So come along and mingle with industry peers, all the the benefit of local charities. You don’t need to donate, just pay for your food… Read More

The Albuquerque Journal had an article about a local company sending silicon carbide wafers into suborbital space to improve their quality. ACME Advanced Materials plans to buy low quality $250 wafers, send them into space using their process, and sell the higher quality wafers for about $750. They are working to add gallium nitride… Read More

Protecting memory with ECC but leaving the rest of an SoC uncovered is like having a guard dog chained up in the back corner of your yard. If the problem happens to be in that particular spot, it’ll be dealt with, otherwise there will be a lot of barking but little actual protection.

Similarly, adding a safety-capable processor like… Read More

There are many facets of our lives that are being driven to a more virtual method of doing things. This is largely due to issues such as scaling due to whatever reason – technical, business, economic. Let’s look at some general cases: In yesteryears people used to travel all the way for face-to-face meetings; today virtual meetings… Read More

Today I was at the Chinese-American Semiconductor Professionals’ Association conference and dinner. Simon Segars, CEO of ARM, gave the dinner keynote. Somewhat surreally, it was in the same room in the same conference center two weeks ago that he gave they keynote at ARM TechCon. In another coincidence, Mike Muller of … Read More

TSMC ♥ Cadence!by Daniel Nenni on 10-11-2014 at 4:30 pmCategories: Cadence, EDA, IP, TSMC

One of the questions I routinely ask amongst the fabless semiconductor ecosystem is, “How are the EDA vendors doing?” There are always complaints because, let’s face it, we all like to complain. On occasion however I do hear about a vendor who goes above and beyond the call of duty and it really brightens my day.

Of late,… Read More

What’s next in test compression?by Beth Martin on 10-10-2014 at 4:45 pmCategories: Events, Siemens EDA

If you’ll be at ITC TestWeek in Seattle (Oct 20-23), here’s one event you don’t want to miss: a technology reception hosted by Mentor, with Janusz Rajski and Nilanjan Mukherjee as the featured speakers. It is free to ITC attendees and you can register here. [If for some crazy reason you haven’t registered for ITC yet, do that… Read More

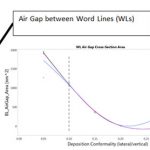

ASML High-NA EUV is Not Ready for High-Volume Production