As I have mentioned before, there are very few secrets in Silicon Valley. Just last week I was minding my own business at a Starbucks when I overheard two engineers complaining about Samsung 14nm shuttles being delayed. They had badges on but I won’t out them because it could have easily been any of the fabless companies in Silicon … Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More

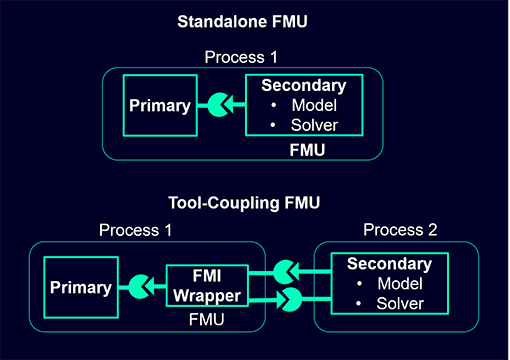

The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read MoreLook who is Leading the World Semiconductor Business

A couple of days ago I was reading a news article which said how long the world economy will be dependent on a single engine to drive it; obviously that single engine is USA. If we consider the overall economy, definitely USA is driving it, and semiconductor is a large part of it. The semiconductor is driving electronics and that is attracting… Read More

Xiaomi Already #3 in Smartphones Behind Samsung and Apple

The Q3 results are mostly in now and there are two big stories. The iPhone 6 of course, which started shipping just before the end of the quarter. The other story is China, now the #1 mobile market in the world. These have led to very different stories for different companies.

Samsung is basically flat with Q2, but that was a big drop. … Read More

Bluetooth Smart Crashes IoT Party

When you hear the term Internet of Things the first image that comes to mind is, well, a lot of things talking over TCP/IP, maybe using WiFi or god forbid Ethernet. But upon closer examination it seems that Bluetooth is crashing the IoT party. This was driven home for me when my girlfriend gave me a FitBit Flex. For those unfamiliar, … Read More

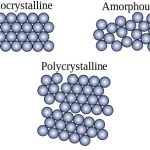

Amorphous Silicon and TFTs

Most ICs are fabricated with crystalline silicon (c-Si), which is a tetrahedral structure forming a well-ordered crystal lattice. There’s another form of semiconductor material called amorphous silicon (a-Si) which has no long-range periodic order. It turns out that a-Si is a great material for the active layer in thin-film… Read More

What does the Ford Mustang and Intel’s Gordon Moore Have in Common with Local Motors?

1964 Vision, Volume and Moore’s Law

The 1964 New York World’s Fair saw Lee Iacocca, then a young 40 year old General Manager, introduce a car that inspired “total performance” and was for a “young America out to have a good time.” This young America would become the baby boomer generation. The Mustang was revolutionary in its affordability,… Read More

Lucio and the Kaufman Award

Tuesday was the Kaufman award dinner. This year it was awarded to Lucio Lanza. Last week I wrote about how Lucio ended up in EDA, although that was not where he finished up. He is currently a venture capitalist running Lanza Technology Ventures, one of the few VCs to make any investments in the EDA/IP/semiconductor space. Also, unlike… Read More

Semiconductor Safety

Semiconductors and automotive are now like peanut butter and jelly. Certainly you can have one without the other but why would you? I remember when a car first talked to me telling me that the door was ajar. It sounded more like, “the door is a jar” but I got the point. Now my car tells me just about everything including what is wrong with… Read More

Daylight Savings Time and the IoT

On Sunday in the USA we changed our clocks back one hour to account for Daylight Savings Time and I was reminded of how far we have to go in getting all of our devices to understand and automatically account for the time. Despite all of the talk about IoT and how it has the promise to automate our lives, we still have to manually set the time.… Read More

MQTT not IoT “god protocol”, but getting closer

One protocol, and its descendants, drove the success of the World Wide Web. IP, or Internet Protocol, is the basis of every browser connection and the backbone of IT data centers. Some assumed that the Internet of Things would follow suit,… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!