As every other person is talking about IoT today, Michael Munsey of Dassault Systemes looks at this trend in the context of critical success factors and Dassault’s strategy towards providing semiconductor solution that integrates the design chain and continues to keep the semiconductor eco-system healthy and profitable. … Read More

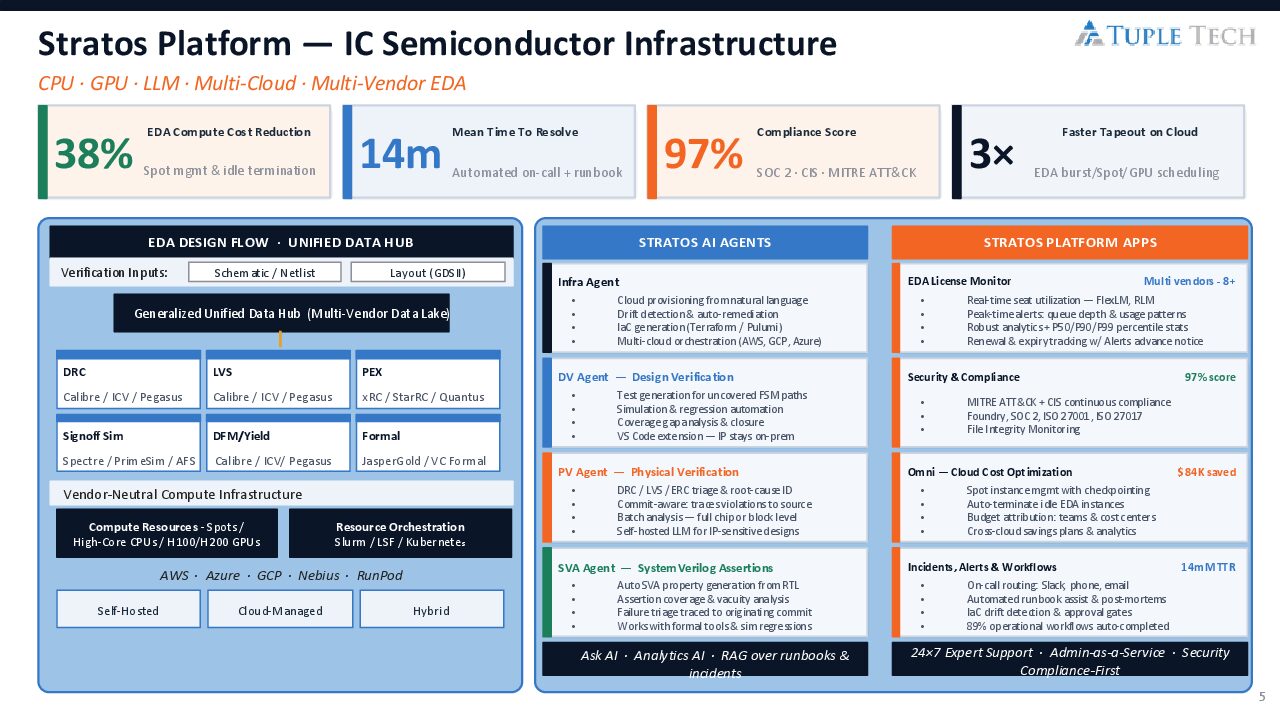

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreVerification plans overcome hope-based coverage

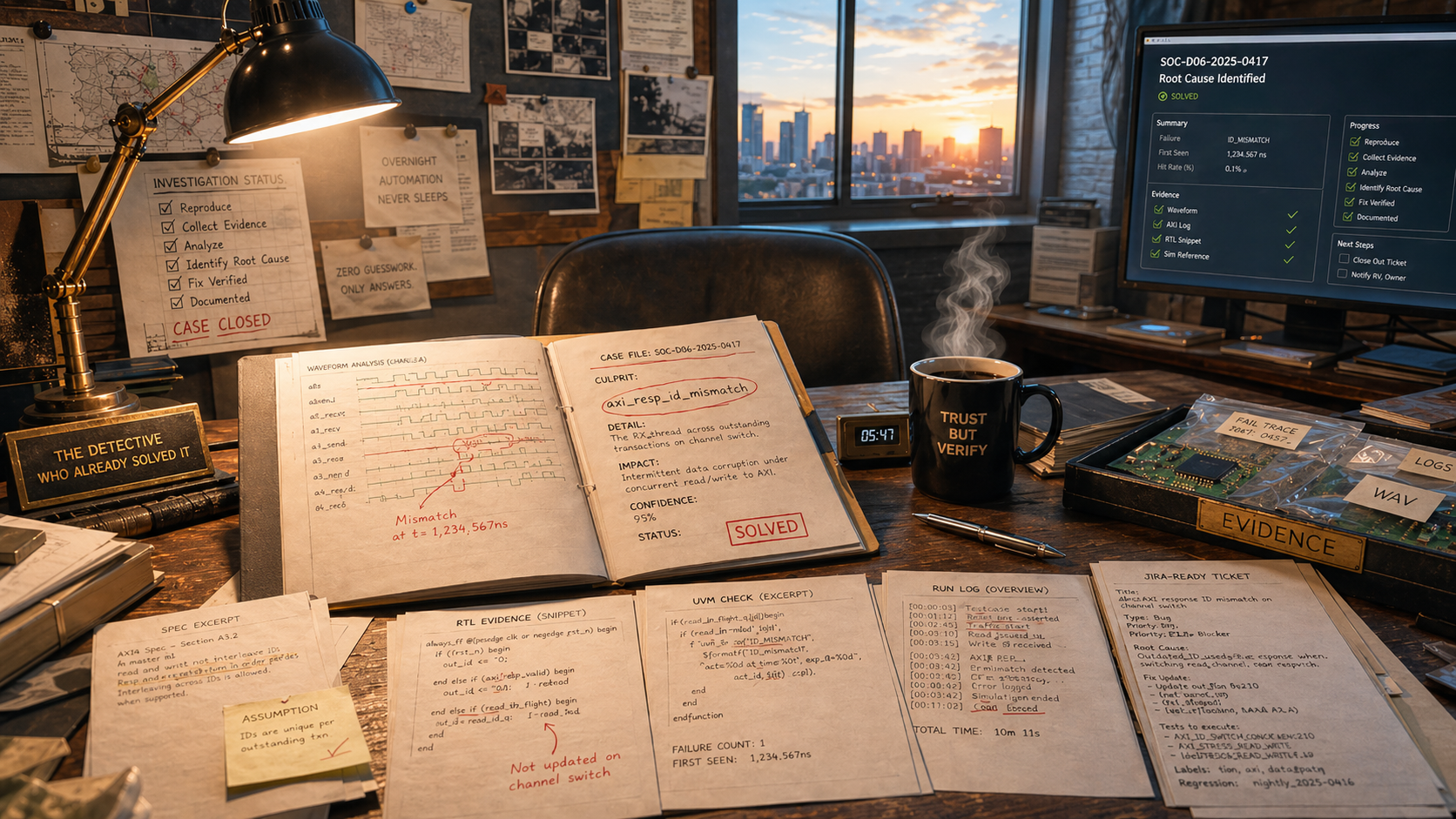

Coverage is an important yet elusive metric for design verification. It often seems 90% of coverage comes with 10% of the effort, and getting the final 10% covered takes the remaining 90% of a project. Usually, it takes another tool or methodology to get at the 10% the first tool missed. With 100% closure difficult, most teams inspect… Read More

IC Design at ZMDI

As a blogger I have the privilege of meeting many IC designers from around the world, mostly through contact on LinkedIn or from connecting at trade shows. Through a contact at DACI met up with Achim Graupner, a manager of methodology and design automation from ZMDI, then asked him for an interview to understand how his group does … Read More

Predicting Component Temperature Early in Design

In today’s electronics with multiple functions working together, heat generation is on the rise; sometimes it becomes intolerable. In fact components running at different temperatures can cause timing issues, and very high temperatures can lead to operational issues such as latch-up. An electronic system can contain chips,… Read More

Xilinx Boards Make a Great Christmas Gift!

Ok, first thing first, Happy Thanksgiving! For the Miller’s as I get older, it is new traditions as some old ones have passed on. Memories are great and new ones to make. So you know the great debate right?

These poor people working Thanksgiving to sell some tablet or smart phone to save a few bucks. Those that must work, my condolences… Read More

Rock for CASA, December 6th

It is the holiday season so time to get together with your friends and colleagues in EDA, IP and semiconductor at the third annual event raising money for Court Appointed Special Advocates (CASA) (www.casaofsantacruz.org). This is the third event that Heart of Technology has worked with CASA. CASA has local organizations and … Read More

‘Tis the season for 4K UHD and HEVC

4K UHD TVs were all dressed up at CES 2014 with no content to show. The good news for the 2014 holiday season is the industry has converged on one set of standards for display, interfacing, and encoding, so consumers should not be left marooned in an instant replay of the 3DTV hype-crash cycle. It may be a bit longer before everyone can… Read More

Transistor-Level IC Design is Alive and Thriving

There’s much talk in EDA about High Level Synthesis (HLS), Transaction Level Modeling (TLM) and the Universal Verification Methodology (UVM), however there’s a lower-level of abstraction, the transistor-level, where high-speed digital cell libraries are created, analog circuits are crafted, and AMS designers… Read More

What makes the world smart?

The simple answer is when everything in the world is smart. But if you think deeply, you would find that the continuous progression to make things easy in life is what makes the world smarter day-by-day – the sky is the limit. In the world of computing, consider the 17[SUP]th[/SUP] century era when humanbrain was used as a computer … Read More

Coverage Driven Analog Verification

Ad hoc digital design verification approaches ran out of steam at least a decade ago when designs got intractably large to make it feasible to keep track of everything with pen and paper and excel. But analog design has remained largely ad hoc to this day. The designer runs spice, looks at the waveforms that come out and decide whether… Read More

Siemens U2U 3D IC Design and Verification Panel