Back in the day, EDA companies enabled the foundries. Seriously, those pesky little foundries chased us EDA companies around like puppies who needed a walk. Now, emerging EDA and IP companies are the puppies and we chase the foundries. Solido Design Automation is one of the hardest working puppies that I have ever helped with strategic… Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

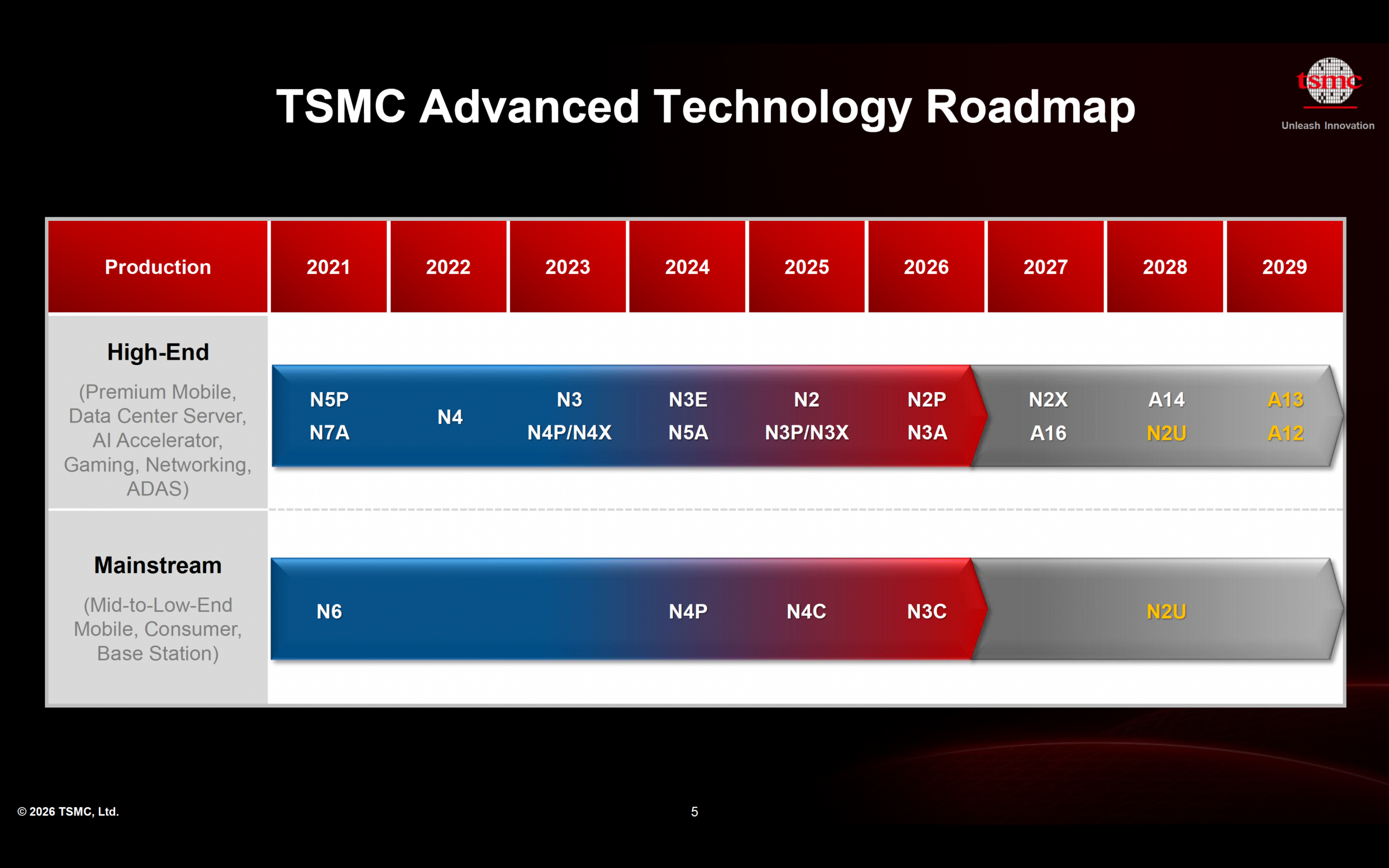

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read MoreTen Things to Do in San Francisco the Way the Locals Do

DAC is in San Francisco, of course, and perhaps you have a day or two to do explore the city. Guidebooks will tell you to visit most of these places but there are much better ways to see them than they typically recommend. Follow these instructions and pretend you are a local.

1. Ride a Cable Car. But don’t wait in line for 45 minutes at Union… Read More

SemiWiki at #52DAC: Nominated for Best Paper Award!

Blogging for Semiwiki is a very good exercise to prepare a paper submission at DAC. Writing a short article using about 600 words to pass one message, and try to deliver this message as clearly as possible. Writing a paper for DAC is very similar, as you have to be synthetic and develop a thesis in 5 slides, no more, as it’s a time limited… Read More

S2C’s Virtex UltraScale Prototyping Provides Designers Much Needed Flexibility

The advent of large system-on-chip (SoC) designs has brought FPGA prototyping hardware into the limelight and the launch of S2C Inc.’s Single VU440 Prodigy Logic Module just shows how far off-the-shelf prototyping has come in a bid to complement hardware verification and software development. Hardware verification… Read More

FD-SOI the Synapse Way

Last week I talked to Marco Brambilla of Synapse Design. Synapse is a design services company headquartered in Silicon Valley. It was founded in 2003 by Satish Bagalkotkar and has been profitable since the beginning. Today it has over 700 people. In addition to the headquarters in Santa Clara, they have a software group in Colorado,… Read More

ClioSoft Celebrates 2014 with 30% Revenue Growth!

One of the first companies we worked with when SemiWiki went live in 2011 was ClioSoft. They had a problem with a competitor spreading misinformation which is certainly not unheard of in EDA. When a company cannot compete technically sometimes they resort to dirty tricks or legal distractions. The first ClioSoft article we published… Read More

How Sidense Sees The Smart Connected Universe

Sidenserecently conducted a webinar on what they call the Smart Connected Universe. They consider the Smart Connected Universe as something that includes a collection of market segments that are both smart and connected. This casts a big net, and includes what many are calling IoT, but goes further into medical, automotive and… Read More

ASMC 2015: GlobalFoundries 22nm SOI plans and more!

The Advance Semiconductor Manufacturing Conference was held on May 3[SUP]rd[/SUP] through May 6[SUP]th[/SUP] in Saratoga Springs, New York. ASMC brings a unique operational perspective to technical conferences related to semiconductors. In this blog I wanted to discuss what I thought was the most interesting paper of the… Read More

MediaTek Breaks the ‘Core’ Barrier, Again

Who says Asian companies can’t innovate? Just look at how Taiwan’s MediaTek Inc. has conceived a 64-bit system-on-chip (SoC) that features 10 Cortex-A cores in a tri-cluster configuration. MediaTek’s Helio X20 processor is also the first mobile SoC that boasts ARM’s latest CPU and GPU cores. Moreover,… Read More

Analog Market Leaders Eyeing on IoT Applications

When we talk about analog IC market, one can easily guess who the leader with lion’s share in the market is. There are also next level leaders with impressive growth rates in this market. The analog market as such is poised to grow with Internet of Things (IoT) because it supplies some of the key components such as data converters, op… Read More

Solving the EDA tool fragmentation crisis