The semiconductor industry is expected to grow at a reasonable pace in 2015 and beyond, with the biggest market being compute applications followed by wireless and consumer applications. The highest growth, however, is expected to be in application-specific products for devices such as smartphones, wearables, memories, … Read More

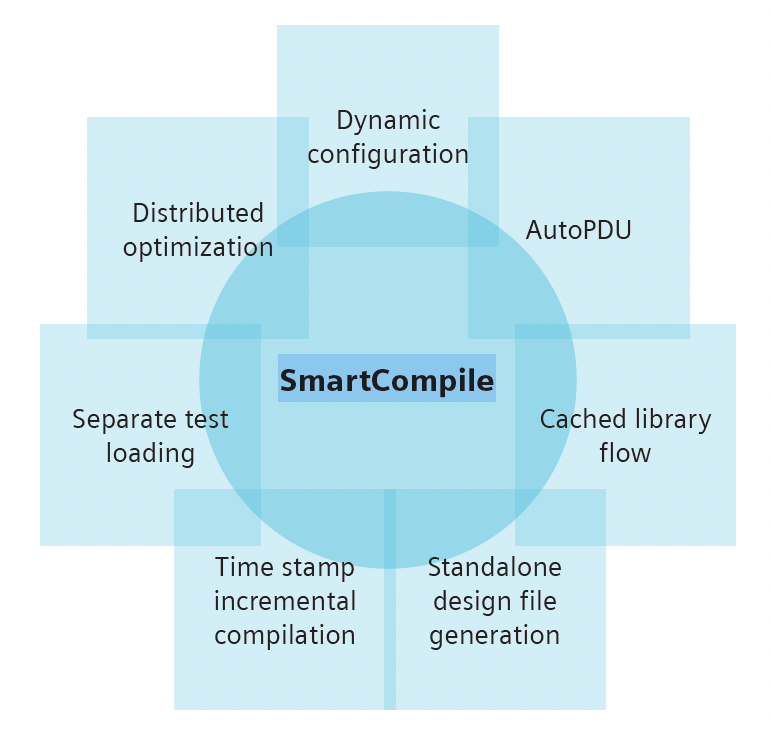

Revolutionizing Simulation Turnaround: How Siemens’ SmartCompile Transforms SoC VerificationIn the race to deliver ever-larger SoCs under…Read More

Revolutionizing Simulation Turnaround: How Siemens’ SmartCompile Transforms SoC VerificationIn the race to deliver ever-larger SoCs under…Read More Arteris Simplifies Design Reuse with Magillem PackagingMany know Arteris as the “network-on-chip”, or NoC,…Read More

Arteris Simplifies Design Reuse with Magillem PackagingMany know Arteris as the “network-on-chip”, or NoC,…Read MoreAgile IC: All You Gotta Do To Join Is…

Back last October 1st was an announcement of Agile IC Methodology. As I said then:Today Sonics has launched the Agile IC Methodology along with several collaborators. The initial phase is to create a LinkedIn group to start the discussion.

See also Agile IC Development

At that point there was just an idea and a LinkedIn group. The… Read More

Shift-West of Semicon Power Centers

It’s true that Japan was once the center of semiconductor business and we were carrying on with that perception until recently. In 1990, six out of top10 semiconductor companies (excluding pure-play foundries) were in Japan; and 59% of worldwide semiconductor market was concentrated with the top10 companies. The semiconductor… Read More

Xtensa Fusion DSP Target IoT including Wireless and Security

Internet of Things (IoT) can be seen as a fashionable buzzword covering so many distinct applications that IoT is sometimes nick-named “Internet of Everything”, or it can be perceived as the next revolution in electronic systems generating more revenues than the smartphone and computer market together in 2020. But the industry… Read More

Imec Technology Forum

I like to quiz people on which country is the one where the most leading edge research on semiconductors is done. People reflexively answer USA or maybe Taiwan or Japan. Nobody who doesn’t already know the answer would pick Belgium. After all the EU headquarters is there not because Belgium is important but because Belgium… Read More

CEVA DSP Cores … Inside Intel

Intel Corp. is gaining discernible market share in the LTE chips business, and Qualcomm, the 800-pound gorilla in the mobile baseband market, suddenly looks in Intel’s crosshairs. A closer look at Intel’s journey from a mobile silicon underdog to the owner of a swelling LTE footprint shows that design ingredients… Read More

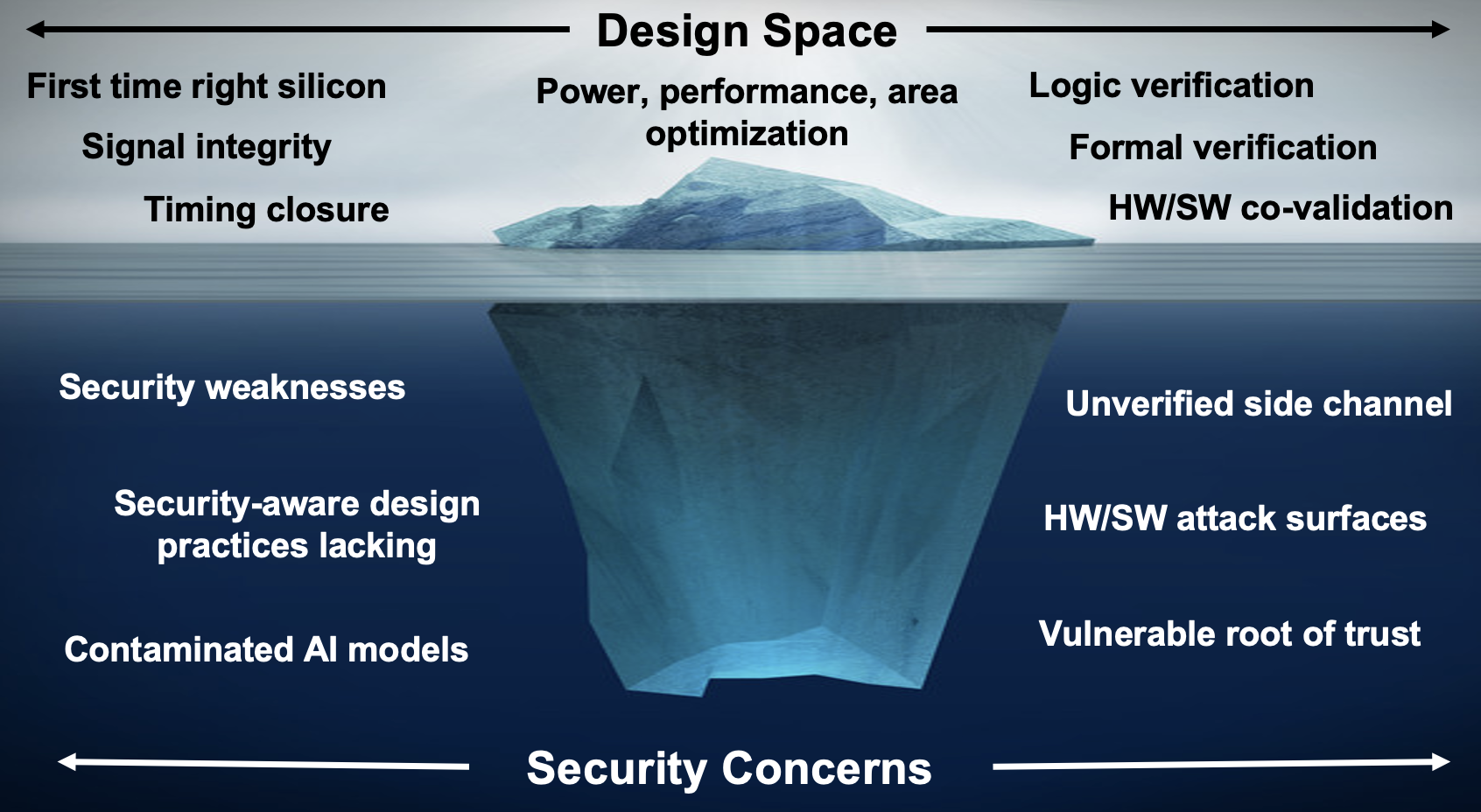

Are There Trojans in Your Silicon? You Don’t Know

Yesterday was the Mentor users’ group U2U. As usual, Wally Rhines gave the keynote, this year entitled Secure Silicon, Enabler for the Internet of Things. Wally started off saying it was a challenge to find a new angle. The number of news articles on cloud computing has exploded from nothing to 72,000 last year. On IoT from … Read More

Moore’s Law is dead, long live Moore’s Law – part 5

In the first four installments of this series we have examined Moore’s law, described the drivers that have enabled Moore’s law and discussed the specific status and issues around DRAM and logic. In this final installment we will examine NAND Flash.… Read More

Moore’s Law is dead, long live Moore’s Law – part 4

In the third installment of this series we discussed the status of DRAM scaling and Moore’s law. In this installment we will tackle logic. The focus will be on foundry logic.

Logic technology challenges

In the second installment of this series we discussed constant electric field scaling. As we mentioned in that installment at … Read More

How is Trillion Sensors by 2025 Panning Out?

From several literatures, talks in the semiconductor industry, forecasts, and BHAGs (Big Hairy Audacious Goals), specifically in the context of IoT (Internet of Things) and IoE (Internet of Everything), we have been looking forward to a world with over a trillion sensors around us. I recollect (produced below) from an impressive… Read More

Moore’s Law Wiki