As I have mentioned before, semiconductor professionals are very smart people, pound for pound the smartest in the workforce in my opinion. So what happens when thousands of engineers from Qualcomm, Broadcom, Altera, and Intel get shown the door? They don’t go to work for Starbucks, they don’t go to the unemployment line, they … Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreWhy I’ll Always Be an Andy Grove Fan

Silicon Valley sadly lost a respected and revered leader with the death of Andrew Grove in March. The co-founder and former CEO of Intel was an inspiration to generations of technologists and business leaders, including me. Andy had a profound influence on me throughout my career. And while I only met him once, I feel as though I’ve… Read More

Ecosystem Partnership for Effective Network Hardware Design

When you’re designing a hardware solution to plug into what is arguably the most complex system of all – the Internet – you can’t get away with a little fake traffic to test whether your box is going to do all the right things at the right performance. You have to model realistic voice, video, data and wireless traffic in… Read More

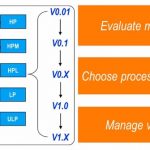

Process Development, CAD and Circuit Design

Working at Intel as a circuit designer I clearly remember how there were three distinct groups: Process Development, CAD and Circuit Design. Each of the groups sat in a different part of the building in Aloha Oregon, we had different job titles, different degrees, spoke with different acronyms and yet we all had to work together … Read More

Webinar alert – VHDL guru says its time to move up

Many years ago when I worked for Ed Staiano at Motorola, I learned never to use the word “comfortable” in a career context. I’m comfortable being with family and friends. This new high-back chair I sit in at my new faux-cocobolo desk (slightly distressed chalk-painted wood and industrial piping, awesome) is comfortable,… Read More

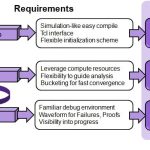

Software-Driven Verification Drives Tight Links between Emulation and Prototyping

I’ve mentioned many times what has become a very common theme in SoC and system verification – it has to be driven by the software because any concept of exhaustively verifying “everything” is neither feasible nor meaningful. Emulation has become a critical component of this flow in validating and regressing… Read More

Bringing Formal Verification into Mainstream

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More

Metric-Driven Verification for System Signoff

Everyone knows that verification is hard and is consuming an increasing percentage of verification time and effort. And everyone should know that system-level verification (SoC plus at least some software and maybe models for other components on a board) is even harder—which is why you see hand-wringing over how incompletely… Read More

Why IoT Needs Fog Computing?

The Internet of Things (IoT) is one of the hottest mega-trends in technology – and for good reason , IoT deals with all the components of what we consider web 3.0 including Big Data Analytics, Cloud Computing and Mobile Computing.… Read More

Solving the EDA tool fragmentation crisis