Tensilica HiFi DSP family, dedicated to voice and audio processing, is shipping over 1 billion units worldwide annually, thanks to the 75+ licensees. The new HiFi 3z architecture offers more than 1.3X better voice and audio processing performance than its predecessor, the HiFi 3 DSP, which leads the industry in the number of audio… Read More

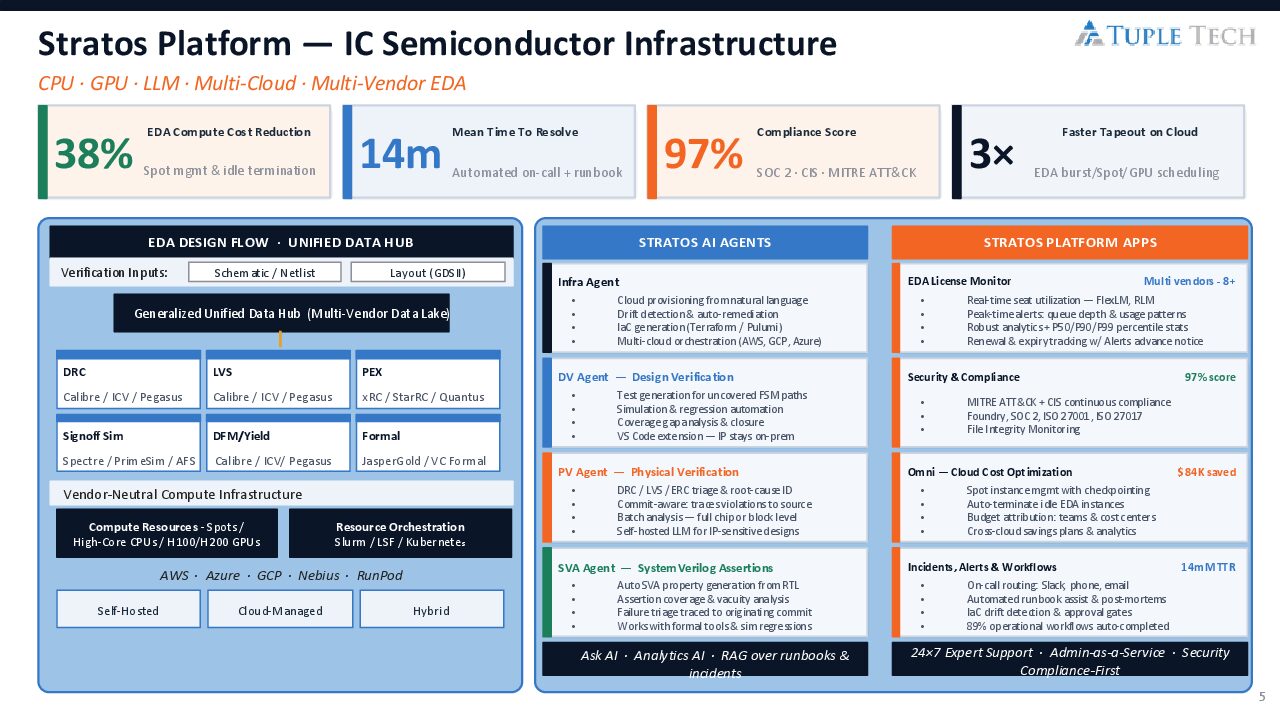

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreSemicap Thoughts: ASML AMAT INTEL SAMSUNG TSMC MICRON

ASML reported results in line and slightly ahead of expectations which helped push ASML and the other semicap stocks back to their original valuations prior to the two step pull back that lasted about a month. We are now back to relatively high, record valuations not seen or ever seen previously (at least for a long time) by many companies.… Read More

A Functional Safety Primer for FPGA – and the Rest of Us

Once in a while I come across a vendor-developed webinar which is so generally useful it deserves to be shared beyond the confines of sponsored sites. I don’t consider this spamming – if you choose you can ignore the vendor-specific part of the webinar and still derive significant value from the rest. In this instance, the topic is… Read More

Connected Car as Data Access Battleground

The big news over the weekend was accusations flying in Europe over German car company anti-competitive collusion. While it’s true that European companies of all sorts are able and inclined to legally share information in a manner that is foreign to U.S.-based companies, proving anti-competitive activity will be a high bar for… Read More

CEO Interview: Chris Henderson of Semitracks

In looking at the SemiWiki analytics over the last six years it is clear that the average age of our readers is trending down. (Yes, Google knows how old we are). The 25-35 age group now represents our largest readership and that is supported by the conferences I have attended recently. At the Design Automation Conference last month… Read More

Emulation makes the What to See List

The analysts at Gary Smith EDA produce an annual What To See List for DAC and I quickly noticed that all three major EDA vendors were included on the list for the specific category of emulation. The big problem that emulation addresses is the ability to run in hardware an early version of your SoC so that software developers can get access… Read More

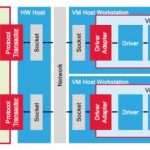

Virtualizing ICE

The defining characteristic of In-Circuit-Emulation (ICE) has been that the emulator is connected to real circuitry – a storage device perhaps, and PCIe or Ethernet interfaces. The advantage is that you can test your emulated model against real traffic and responses, rather than an interface model which may not fully capture… Read More

Seeking Autonomy

I’d wager that if I mention autonomous vehicles, the first thing that you would think of would be autonomous cars. The truth is that we will see many other kinds autonomous vehicles in the years ahead. Their applications will range from package delivery to saving lives on the battlefield. Of course, to some extent they are already… Read More

The Transformation of Silvaco!

Founded in 1984, Silvaco is now the largest privately held EDA company with a rich history including a recent transformation that is worth a blog if not a book. Coincidently, I started my career in Silicon Valley in 1984 and have had many dealings with Silvaco over the years including a personal relationship with Silvaco founder … Read More

Webinar: Ansys on Multi-Physics PDN Optimization for 16/7nm

On the off-chance you missed my previous pieces on this topic, at these dimensions conventional margin-based analysis becomes unreasonably pessimistic and it is necessary to analyze multiple dimensions together. People who build aircraft engines, turbines and other complex systems have known this for quite a long time. You… Read More

Siemens U2U 3D IC Design and Verification Panel