I will be pleased to moderate on December 7[SUP]th[/SUP] the Open-Silicon webinar addressing the benefits of the multi-channel multi-rate forward error correction (MCMR FEC) IP and the role it plays in high-bandwidth networking applications, especially those where the bit error rate is very high, such as high speed SerDes … Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreOutsourced Operations: Reduced Risk, Fast Ramp, and Managed Complexity

One of the more interesting semiconductor success stories is Apple and how they transformed from a struggling computer company to a dominant chip maker. We covered this story in quite a bit of detail in our book “Mobile Unleashed” in Chapter 7 “From Cupertino” but the short answer to how they did it is: Outsourced Operations.

Apple’s… Read More

Field-Solver Parasitic Extraction Goes Mainstream

Layout parasitic extraction (LPE) has three primary goals – accuracy, capacity, and throughput. Traditionally, LPE tools have offered two methods for capacitance derivation, with tradeoffs on these goals:… Read More

CEVA and Local AI Smarts

When we first started talking about “smart”, as in smart cars, smart homes, smart cities and the like, our usage of “smart” was arguably over-generous. What we really meant was that these aspects of our daily lives were becoming more computerized and connected. Not to say those directions weren’t useful and exciting, but we weren’t… Read More

Protecting electronics around the world, SEMI insights

SEMI is a worldwide organization with local chapters like the one here in Oregon, where I attended a recent half-day presentation by several industry experts on the topic – Globalization, How it shapes the Semiconductor industry:

- Michael Chen, Director, Mentor – A Siemens Business

- John Brewer, CEO, Amorphyx

- Ed

Advanced ASICs – It Takes an Ecosystem

I remember the days of the IDM (integrated device manufacturer). For me, it was RCA, where I worked for 15 years as the company changed from RCA to GE and then ultimately to Harris Semiconductor. It’s a bit of a cliché, but life was simpler then, from a customer point of view at least. RCA did it all. We designed all the IP, did the physical… Read More

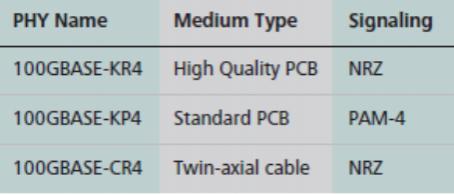

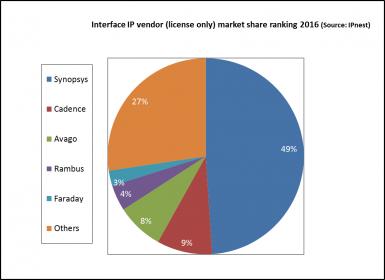

Worldwide Interface IP Revenue Grew by 13.5% in 2016 (Source: IPnest)

IPnest has released the 9[SUP]th[/SUP] version of the Interface IP Survey, ranking by protocol the IP vendors addressing the Interface segments: USB, PCI Express, (LP)DDRn, MIPI, Ethernet & SerDes, HDMI/DP and SATA. When the 1[SUP]st[/SUP] version has been issued in 2009, the IP segment was weighting $225 million and the… Read More

Seeking Solution for Saving Schematics?

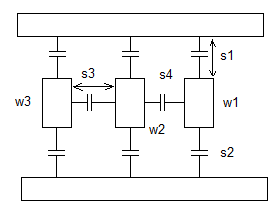

Schematics are still the lynchpin of analog design. In the time that HDL’s have revolutionized digital design, schematics have remained drawn and used much as they have been for decades. While the abstraction of HDL based designs has made process and foundry porting relatively straightforward, porting schematic based designs… Read More

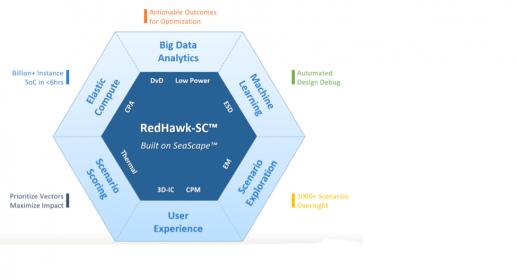

Big Data Analytics and Power Signoff at NVIDIA

While it’s interesting to hear a tool-vendor’s point of view on the capabilities of their product, it’s always more compelling to hear a customer/user point of view, especially when that customer is NVIDIA, a company known for making monster chips.

A quick recap on the concept. At 7nm, operating voltages are getting much closer… Read More

7nm SERDES Design and Qualification Challenges!

Semiconductor IP is the fastest growing market inside the fabless ecosystem, it always has been and always will be, especially now that non-traditional chip companies are quickly entering the mix. Towards the end of the year I always talk to the ecosystem to see what next year has in store for us and 2018 looks to be another year of … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center