I’m an avid road bike enthusiast having just completed my 2017 goal of 13,000 miles, so follow me on Strava if you want to see the routes and photo adventures I have in Oregon. In the photo below I’m the guy in the middle with the Portland Velojersey on and we’re in a parking lot just 2 blocks away from Intel’s… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreThe lofty rise of the lowly FPGA

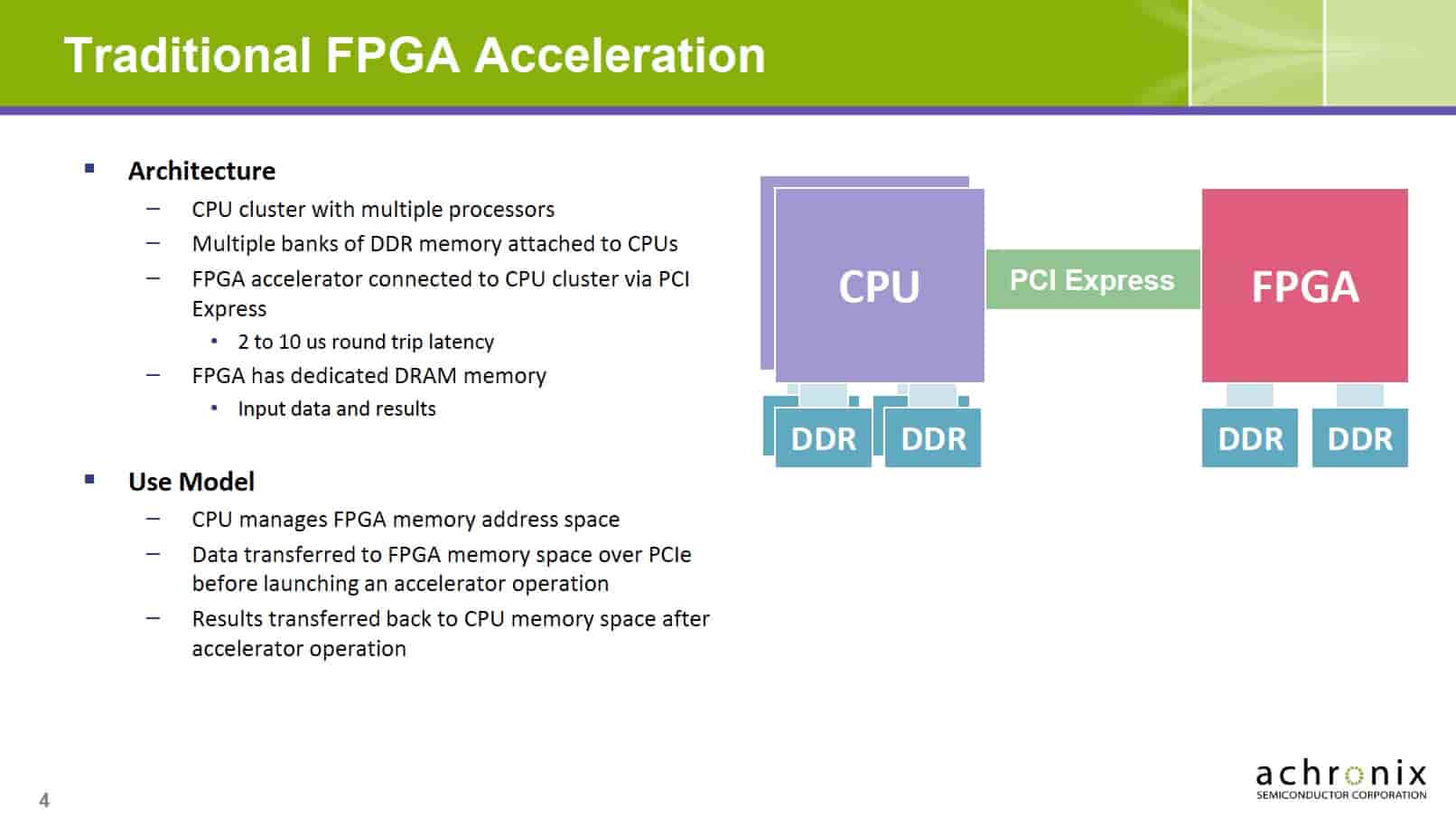

FPGA programmable logic has served in many capacities since it was introduced back in the early 80’s. Recently, with designers looking for innovative ways to boost system performance, FPGA’s have moved front and center. This initiative has taken on new urgency with the slowing down of process node based performance gains. The… Read More

French Tech at CES, 2nd country after USA with 274 Start-Up at Eureka Park!

France exposure will be very strong at Las Vegas CES this year, the 3[SUP]rd[/SUP] country with 365 companies, behind USA and China. If you just take the start-up number into account, 274 French start-ups will be present, just behind the USA with 280 start-ups! If you look back, it’s a great jump compared with 2017 (178 start-up) … Read More

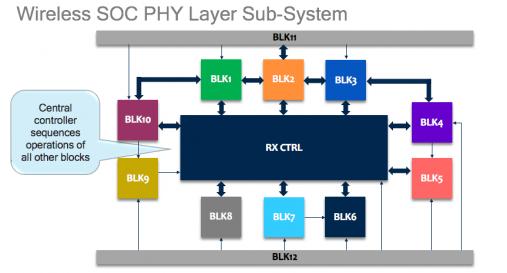

System Level Formal

Two recently announced vulnerabilities in major processor platforms should remind us that bugs don’t organize themselves to appear only in domains we know how to test comprehensively. Both Meltdown and Spectre (the announced problems) are potential hardware system-level issues allowed by interactions between speculative… Read More

FinFET ASICs for Networking, Data Center, AI and 5G

On the heels of successful seminars in Tokyo and Shanghai, eSilicon is starting the new year back in the cloud with a webinar version of the live events for those, like myself, who could not attend. The webinar will compress the 3 hour live event into 60 minutes which will provide a great place to start a conversation on your next chip… Read More

CEVA ClearVox Simplifies Voice Pickup

Voice-based control is arguably becoming another killer app, or killer app-enabler in the very significant shifts we are seeing in automation. After a bumpy start in car feature control (for navigation, phone calls, etc) and early smartphone “intelligent” assistants, voice-based interfaces now seem to be maturing into a genuinely… Read More

Getting Started with RISC-V

As I mentioned before, SiFive and RISC-V are trending topics on SemiWiki.com which makes complete sense since we have been covering semiconductor IP and ARM since we first went online in January of 2011.

In total we have published 707 IP related blogs that earned 3,565,140 views (5043 views per blog average). Out of that, 254 are … Read More

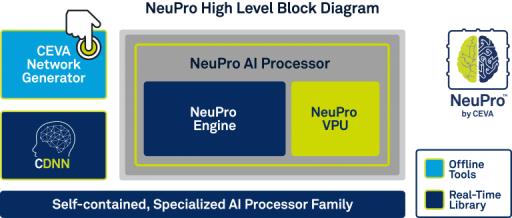

CEVA Ups the Ante for Edge-Based AI

AI is quickly becoming the new killer app and everyone is piling on board as fast as they can. But there are multiple challenges for any would-be AI entrepreneur:

- Forget about conventional software development; neural nets require a completely different infrastructure and skill-sets

- More and more of the interesting opportunity

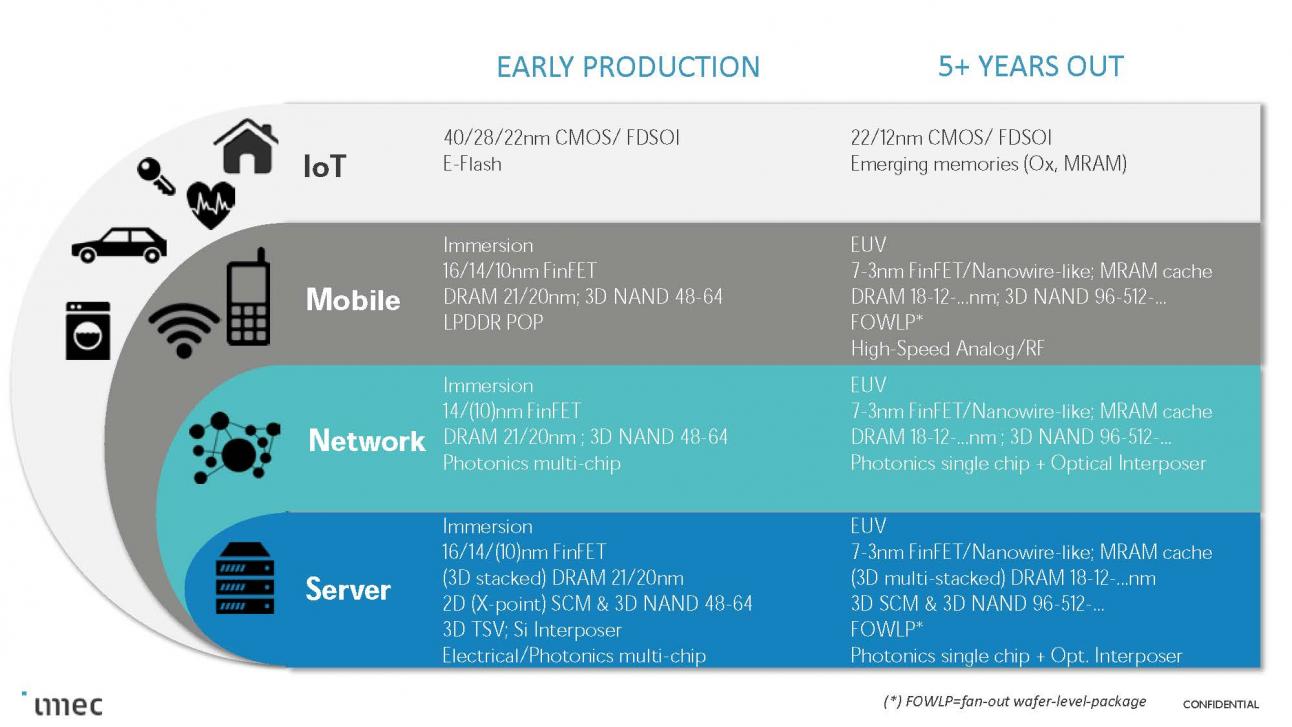

IEDM 2017 – imec Charting the Future of Logic

At the IEDM 2017, imec held an imec technology forum and presented several papers, I also had the opportunity to interview Anda Mocuta director of technology solutions and enablement. In this article I will summarize the keys points of what I learned about the future of logic. I will follow this up with a later article covering memory.… Read More

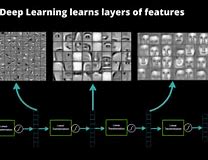

How Deep Learning Works, Maybe

Deep learning, modeled (loosely) on the way living neurons interact, has achieved amazing success in automating recognition tasks, from recognizing images more accurately in some cases than we or even experts can, to recognizing speech and written text. The engineering behind this technology revolution continues to advance… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era